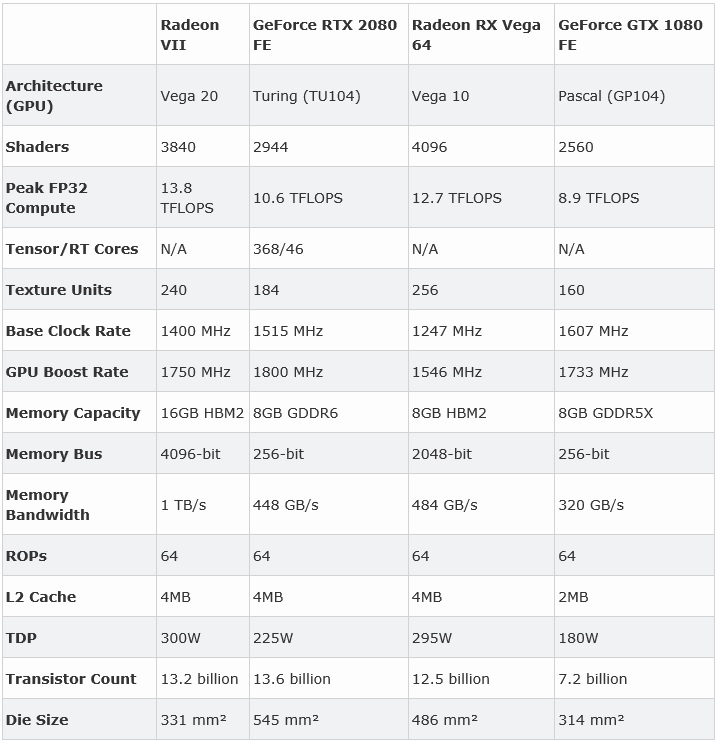

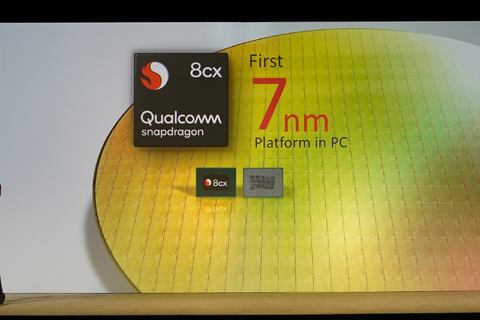

첨단 로직 반도체 양산을 위한 EUV(Extreme Ultra-Violet:극 자외선) 노광 기술의 미래 그림이 드러났다. 7nm세대 기술 노드부터 양산을 올해(2019년)를 시작으로 2년~3년의 간격으로 차세대 기술 노드로 이행한다.

즉 5nm세대의 양산 개시는 2021년, 3nm세대의 양산 개시가 2023년이라는 것은 EUV 노광 기술의 개발이 비교적 순조롭게 진행되었을 때의 스케줄이다. 다시 다음 세대인 2nm세대 기술 노드에 대해서는 다소 모호하다. 양산 개시 시기는 빨라도 2026년이 될 것으로 보인다.

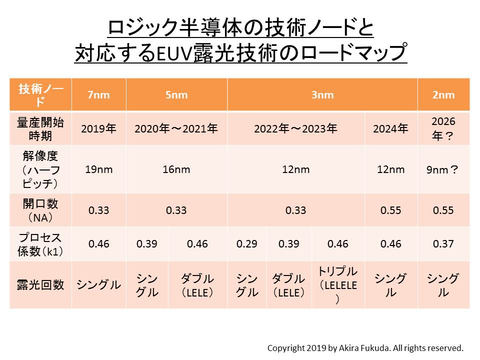

해상도(하프 피치)를 결정하는 것은 파장과 개구수, 프로세스 계수

기술 노드의 이행은 반도체 노광 기술의 해상도(하프 피치) 향상이 이끈다. ArF 액침노광 기술이나 EUV 노광 기술 등의 해상도(R)는 노광의 파장(λ)에 비례하고 광학계의 개구 수(NA)에 반비례한다. 즉 해상도를 높이려면 파장을 짧게 하고 개구 수를 불리는 것이 필요하다. 실제로는 "프로세스 계수(k1)"로 불리는 상수에도 해상도는 비례한다. 이 프로세스 계수를 낮추면 해상도가 올라간다. 다만 프로세스 계수의 최소 한계치는 0.25, 앞 이하로 할 수 없다.

ArF 액침노광 기술이나 EUV 노광 기술 등에서는 광원의 파장이 고정되어 움직일 수 없다. 덧붙여 ArF 액침노광의 파장은 193nm, EUV 노광의 파장은 13.5nm. 양자에게 10배를 넘는 격차가 있어 단순 계산에서 EUV 노광이 압도적으로 유리한 것을 알 수 있다.

ArF 노광 기술까지의 이른바 광 리소그래피(노광)기술에서는 개구수를 높이는 것이 해상도 향상의 유력한 수단이 되어 왔다. 구체적으로는 노광 장치인 스테파나 스캐너 등의 광학계를 개량함으로써 개구수를 상승시켜 왔다.

이것에 비해 EUV 노광 기술은 개구수는 별로 움직일 수 없다. X선의 반사 광학계를 사용하는 EUV 노광기술에서는 광학계가 매우 복잡한 구조로 되어 있으며 광학계의 변경은 막대한 개발투자를 수반한다. 이 때문에 EUV 노광 장치로 개구수가 변경된 것은 과거에 한 번 밖에 없다. 초기 EUV 스캐너의 개구수는 0.25이며 현행 기종의 개구수는 0.33이다. 모두 ArF 드라이 노광의 최고치인 0.93에 비하면 상당히 낮다.

그리고 향후 몇 년은 개구수가 0.33의 EUV 스캐너를 사용하면서 해상도를 높여 간다. 바꿔 말하면 같은 개구수의 노광 장치로 하프 피치를 미세화해 나가게 된다.

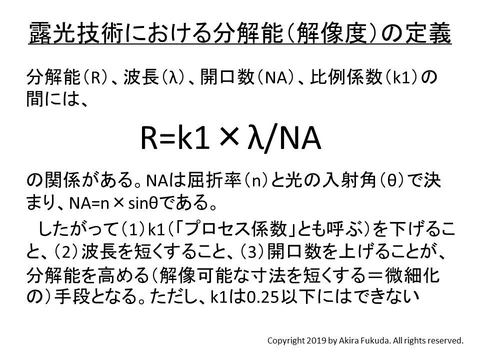

프로세스 계수를 단계적으로 낮춰 해상도를 높이다

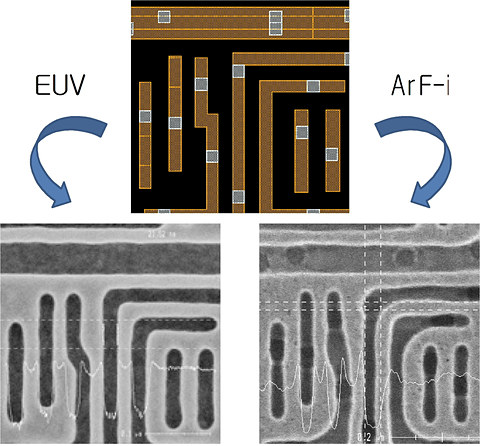

이 때문에 미세화의 기법은 상당히 한정되어 있다. 파장과 개구 수가 고정되어 있으므로 나머지는 프로세스 계수밖에 없다. 광학적으로는 프로세스 계수를 줄이는 것으로 해상도를 향상시킬 수 있고, ArF 액침노광 기술과 마찬가지로 멀티 패터닝 기술과 조합함으로써 프로세스 계수를 실질적으로 내리는 수법이 사용된다. 그리고 기계적으로는 노광 장치의 중첩 오차를 줄일 필요가 있다.

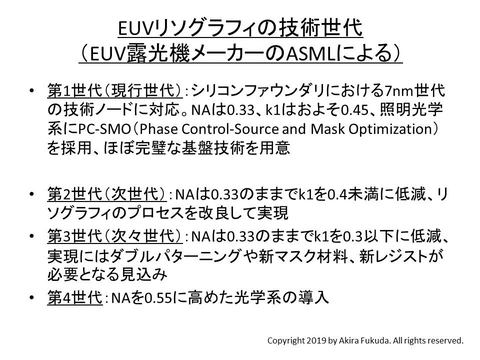

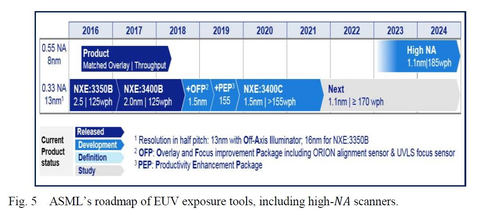

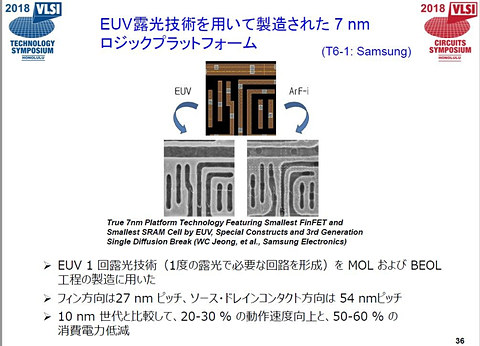

EUV 노광 장치 제조사인 ASML은 EUV 노광 기술의 향후 미세화를 4가지 기술 세대로 나누어 논하고 있다. 현행 세대가 제 1세대로 7nm 로직 양산에 적용되는 세대이기도 하다. 프로세스 계수는 0.45 안팎이다.

이어 2세대에서는 프로세스 계수를 0.40 미만으로 낮춘다. 노광 기술 하드웨어(광학)계와 소프트웨어(레지스트)를 개량함으로써 실현한다. 기본적으로 현행 기술의 개량이다.

그리고 제 3세대에서는 프로세스 계수를 0.30 아래로 낮춘다. 실현에는 현행 기술의 개량만으로는 어려운 멀티 패터닝 기술과 새로운 재료의 마스크, 새로운 재료의 레지스트라는 요소 기술의 도입이 필요하다고 한다. 또 제 4세대에서는 프로세스 계수를 내리지 못하는 점에서 개구 수를 0.55로 높인 광학계를 개발한다.

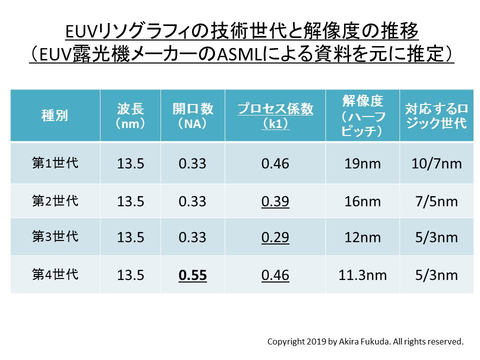

ASML이 공표한 기술 세대의 자료에서는 프로세스 계수의 값이 구체적으로는 기술되어 있지 않다. 거기서 가의 값을 입력함으로써 해상도가 어느 정도까지 향상되는지를 계산해 보면 현행 세대(제 1세대)의 프로세스 계수가 0.46이라고 하면 대응하는 해상도(하프 피치)는 19nm.

제 2세대 프로세스 계수는 0.39로 하면 대응하는 해상도는 16nm. 최첨단 로직기술 노드라면 7nm세대에서 5nm세대의 양산에 적용할 수 있다. 제 3세대 프로세스 계수는 0.29로 하면 대응하는 해상도는 12nm. 최첨단 로직기술 노드는 5nm세대에서 3nm세대의 양산에 적용할 수 있다.

그리고 제 4세대에서는 광학계의 개구수가 대폭 바뀌므로 프로세스 계수는 제 1세대와 같은 0.46으로 가정하면 개구수가 0.55이면 프로세스 계수가 0.46으로 크더라도 대응하는 해상도는 제 3세대와 거의 같은 11.3nm.

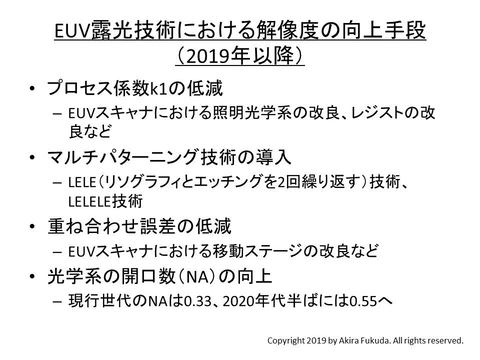

EUV 노광기술 멀티패터닝 도입

광학계나 레지스트 등의 노광기술을 개량하지 않고 프로세스 계수k1을 실질적으로 낮추는 유력한 방법이 멀티패터닝(다중노광)기술이다. ArF 액침노광으로 널리 보급된 멀티패터닝 기술을 EUV 노광기술에서도 채택하는 것이 검토되고 있다.

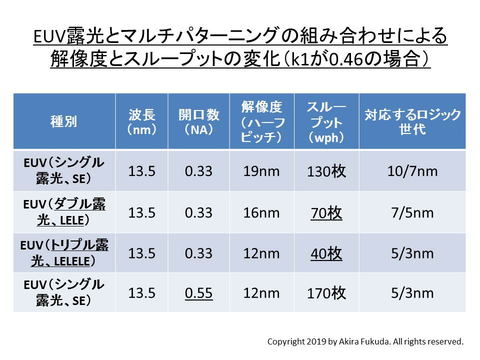

예를 들어 더블노광에서는 리소그래피(L)와 에칭(E)을 2회 반복하는 LELE 기술을 도입한다. 프로세스 계수가 0.46에 EUV 노광기술(개구수는 0.33)에 LELE 기술을 도입하면 해상도(하프피치)는 16nm로 줄어든다. 싱글 노광으로 프로세스 계수를 0.39로 낮춘 것과 같은 효과를 얻을 수 있게 된다.

또한 트리플 노광에 리소그래피(L)와 에칭(E)을 3회 반복하는 LELELE 기술을 도입하면 싱글 노광으로 프로세스 계수를 0.29로 낮춘 것과 같은 효과를 얻을 수 있게 된다.

단 멀티패터닝 기술에서는 스루풋이 저하된다. 싱글노광(SE 기술)에서 웨이퍼 처리장수(시간당)를 130장으로 하면 더블노광(LELE 기술)에서는 70장으로 절반 가까이 떨어진다. 트리플 노광(LELELE 기술)이라면 스루풋은 40매로 싱글 노광의 3분의 1 이하가 되어 버린다.

요약하면 다음 세대인 5nm기술 노드에서는 싱글 노광을 유지하면서 프로세스 계수를 0.39로 낮추는 방향과 더블 노광(LELE 기술) 채용에 의해 실질적으로 프로세스 계수를 낮추는 방향이 있다. 모두 해상도는 16nm이다. 양산 개시 시기는 2021년이라고 예측되며 더블 노광을 채용하면 2020년으로 앞당겨 양산에 들어갈 수 있을 것이다.

차차 세대인 3nm기술 노드는 좀 더 복잡해진다. 싱글 노광에서 프로세스 계수를 0.29로 낮추는 방향과 더블 노광(LELE 기술)과 프로세스 계수가 0.39 노광 기술을 조합하는 방향, 그리고 트리플 노광(LELELE 기술)을 채용하는 방향이 있다. 모두 해상도는 12nm. 양산 개시 시기는 2023년이라고 예측된다. 다만 트리플 노광을 채용하면 양산 개시 시기는 빨라질 가능성이 있다.

또 다음 세대인 2nm기술 노드는 개구 수가 0.33의 EUV 노광 기술에서는 실현이 어렵다고 본다. 개구 수를 0.55로 높인 EUV 노광 기술의 실용화를 기다려야 할 것이다.

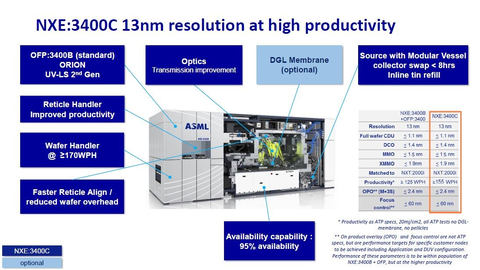

EUV 노광장치 중첩 정밀도와 생산성을 개량

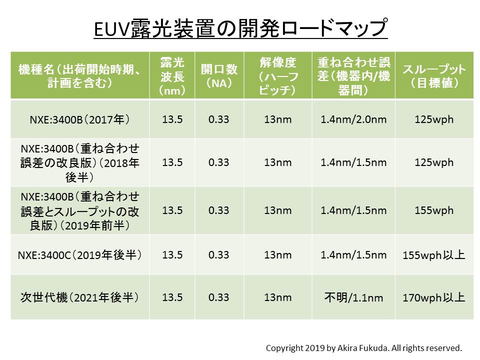

EUV 노광 기술 개발에서 매우 중요한 것이 EUV 노광 장치(EUV 스캐너)개량이다. EUV 노광 장치 제조사인 ASML은 출하 중인 7nm세대용 양산용 EUV 스캐너 "NXE:3400B"에 이어개발 로드맵을 공개한 바 있다.

그 로드맵에 따르면 "NXE:3400B"를 바탕으로 오차를 줄인 버전을 개발한다. 다음에 오차를 줄인 버전을 바탕으로 산출량(생산성)을 높인 버전을 개발하고, 올해(2019년)전반까지 이들의 개량을 완료시킨다.

이어 이들 개량의 성과를 넣은 신기종 "NXE:3400C"를 개발하고, 올해 연말까지 출하를 시작한다. "NXE:3400C"는 5nm세대의 본격적인 양산을 짊어질 것으로 보인다.

그리고 중합 오차를 낮춤과 함께 산출량을 더 높인 "차세대기"의 개발을 예정하고 있다. 차세대기의 형명은 밝히지 않았다. 출하 개시 예정 시기는 2021년 후반이다. "차세대기"는 3nm세대의 양산을 짊어질 것이다.

이러한 EUV 노광 장치는 모두 개구수가 0.33의 광학계를 탑재한 기종이다. ASML은 이와 함께 개구수를 0.55로 높인 EUV 노광장치 개발에 본격 나서고 있다.

"High NA"라 ASML이 부르는 개구수 0.55의 EUV 스캐너의 출하 개시 시기는 2023년 후반이라고 하는 것이 현재의 스케줄이다. 최초의 개발장치 완성은 2021년 연말을 예정한다. 'High NA' 장치 개발 상황에 대해서는 본 칼럼에서 다시 한 번 언급하고자 한다.

출처 - https://pc.watch.impress.co.jp/docs/column/semicon/1164527.html