완성에 가까워진 삼성 EUV 리소그래피 7나노 기술

Samsung Electronics(이후 "Samsung"으로 표기)는 미세 가공에 EUV(Extreme Ultra-Violet:극 자외선) 리소그래피를 채용한 7nm세대 반도체 양산 기술을 개발 중이다.

이 양산 기술이 거의 완성 단계에 다가왔다. 2018년 말까지 제품 칩(모바일 애플리케이션 프로세서 예상) 양산을 시작할 전망이다.

Samsung은 이전부터 7nm세대의 반도체 생산에 EUV 리소그래피를 도입하겠다고 밝혔다. 지난해(2017년) 2월에 개최된 반도체 회로 기술 국제 학회 "ISSCC 2017"에서 EUV 리소그래피를 도입하고 SRAM 개발 칩(기억 용량 8Mbit)를 공표했다.(강연 번호 12.2)

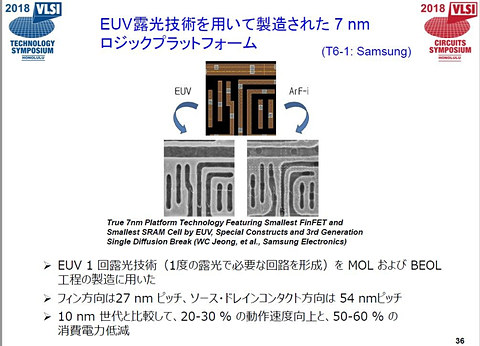

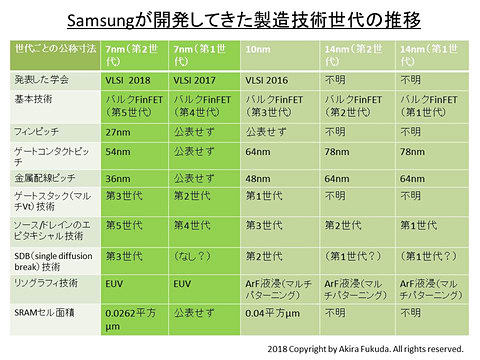

2017년 6월에는 반도체 기술 국제 학회 "VLSI 포럼"에서 EUV 리소그래피를 채용한 7nm세대의 반도체 제조 기술을 공표했다.(강연 번호 T6-1) 이들을 "제 1세대" EUV 채용 7nm제조 기술이라고 Samsung에서 호칭하고 있다.

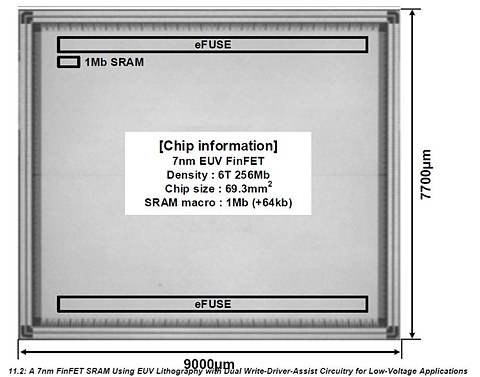

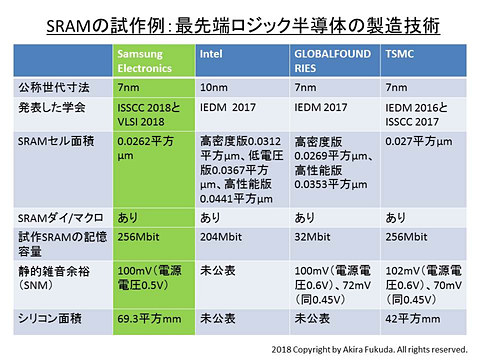

Samsung이 양산용으로 만들어 온 것은 "제 2세대" 7nm 제조 기술이다. 2018년 2월에 국제 학회 ISSCC에서 256Mbit로 기억 용량을 대폭 확대한 SRAM 실리콘 다이를 개발했다.(강연 번호 11.2)

그리고 올해 6월 20일(현지 시간) 미국 하와이 호놀룰루에서 열린 VLSI 포럼에서 제 2세대 EUV 채용 7nm 제조 기술의 개요를 공표했다.(강연 번호 T6-1)

콘택트와 최소 피치 배선 가공에 EUV 리소그래피 적용

EUV 리소그래피를 적용한 것은 제 1세대와 마찬가지로 트랜지스터(FinFET)와 메탈 배선을 연결하는 MOL(Middle-Of-Line 콘택트) 층과 최소 피치 메탈 배선(Mx)층이다. 게이트 피치(CPP) 54nm, 메탈 배선 최소 피치는 36nm으로 상당히 좁다. 모두 EUV 싱글 노광으로 알려졌다.

트랜지스터는 벌크 실리콘 FinFET이다. 핀은 27nm로 극단적으로 작으며 이쪽은 ArF 액침 노광과 SAQP 기술을 조합해 가공했다. 트랜지스터 전압은 제 1세대와 마찬가지로 3종류를 내놓았다. 전압은 높은 측에서 "RVT(Regular Voltage Threshold)", "LVT(Low Voltage Threshold)", "SLVT(Super Low Voltage Threshold)"라고 부르며 구분된다.

EUV 리소그래피의 진가는 밀도가 아닌 가공 패턴의 충실도

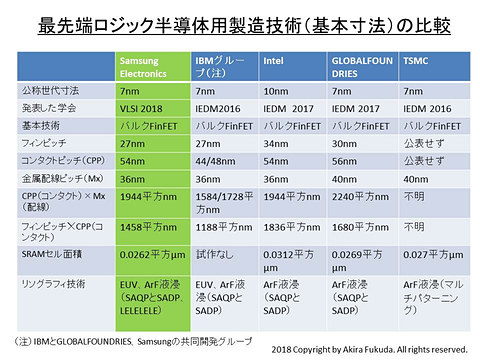

제 2세대 7nm 제조 기술을 타사가 과거에 국제 학회에서 발표한 7nm 제조 기술(Intel 10nm) 제조 기술과 비교하면 핀은 타사의 최소와 같거나 메탈 배선 피치는 타사와 최소 동등하며 콘택트 피치는 타사의 최소보다 느슨하다.

로직 셀의 밀도 기준이 되는 CPP(게이트 피치)×배선 피치의 면적과 트랜지스터의 밀도 기준이 되는 핀 피치×CPP의 면적은 상당히 작지만 타사의 최소치보다 다소 크다. SRAM의 메모리 셀 면적은 타사의 SRAM 보다 작은 과거 최소를 기록했다.

이들 수치를 보자면 EUV 리소그래피 도입에 의해 Samsung의 7nm 제조 기술이 타사에 비해서 로직 회로 밀도가 특히 높아지거나 트랜지스터의 밀도가 특별히 향상되는 점은 사라졌다.

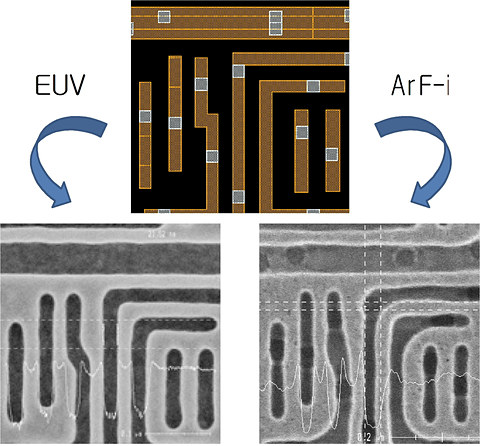

실제로 강연에서 Samsung은 SRAM 셀들이 세계 최소인 것은 어필했지만 논리 회로의 밀도에 대해서는 타사와 비교한 우위성 주장이 보이지 않았다. EUV 리소그래피 도입에 따른 우위성에 Samsung이 강하게 주장했던 것은 가공 패턴의 충실도가 현격히 향상되는 것이다. ArF 액침에 비하면 마스크 패턴에 대한 충실도는 70% 향상이 있다고 한다.

충실도의 비약적인 향상으로 인한 가장 중요한 진화는 구부러진 배선 패턴을 가공할 수 있게 만드는 것이다. 이 때문에 배선 레이아웃의 자유도가 대폭 향상된다. 그 결과 배선 지연이 단축되고 배선의 층 수가 감소하며 로직 셀들이 작아진다.

ArF 액침 멀티 패터닝에서는 구부러진 배선 패턴의 가공이 어렵고 배선 패턴은 평행 직선 군이었다. 예를 들어 제 1층과 제 3층의 배선이 수평 방향의 평행 직선 군이라면 제 2층과 제 4층의 배선은 수직 방향의 평행 직선 군이 되도록 했었다.(직교 패턴)

신호 전송 경로(레이아웃)로 상층 혹은 하층의 배선층에 신호를 교환할 필요가 있는데 이것은 배선 면적 증대와 배선 저항의 증대, 비어에 의한 저항 증대라는 문제를 발생시킨다. EUV 리소그래피에 의한 효과는 콘택트의 치수 차이와 배선간 공간의 치수가 대폭 줄어든다는 것이다.

Samsung의 발표 논문에 따르면 ArF 액침(멀티 패터닝)에 비해 콘택트의 치수는 약 절반으로 배선간 공간의 치수는 약 3분의 2로 줄었다. 편차의 감소는 설계 상의 치수를 더 줄일 여유를 가져와 이것도 로직 셀의 축소로 이어지고 있다. VLSI 포럼 강연에서는 로직 셀(표준 셀)의 높이가 10% 정도 짧아진다고 설명하고 있었다.

10nm세대에 비해 속도는 20~30% 향상, 소비 전력은 30~50% 저감

Samsung이 개발한 7nm세대의 제조 기술은 동사의 10nm세대에 비해 속도, 소비 전력이 함께 개량되고 있다. 트랜지스터 레벨(제 1세대 7nm기술)에서는 속도가 20% 향상되고 소비 전력이 35% 감소했다.

로직 셀 라이브러리 레벨(제 2세대 7nm기술)이 되면 속도가 20%~30% 향상되고 소비 전력은 30%~50% 가량 감소한다고 한다. 또 CPP와 배선 피치 곱의 면적은 10nm세대에 비해 63%로 축소했다.

모바일 애플리케이션 프로세서가 최초의 제품이 될 전망

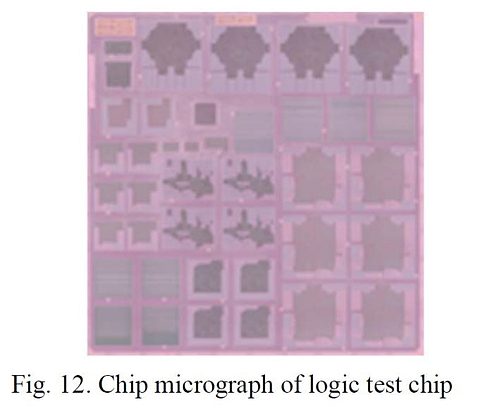

강연에서 주목된 것은 EUV 채용 7nm세대 최초의 제품이 될 것으로 보이는 모바일 애플리케이션 프로세서를 개발한 실리콘 다이 사진을 보인 것이다.

고의로 만든 듯한 흐릿한 사진이기 때문에 세부적으로 확인하기 어렵게 하고 있었다. 실리콘 다이 면적은 공개하지 않았다. 개발한 애플리케이션 프로세서는 복수의 CPU 코어와 복수의 GPU 코어, SRAM 매크로를 내장한다. 개발 생산면에서 완제품을 이미 봤다는 것이다.

그 외 강연에서는 장기 신뢰성 테스트 [NBTI] 테스트와 절연막 시간 경과 파괴 [TDDB] 테스트에서 10년 이상의 수명 보증이 가능하다고 밝혔다. EUV 리소그래피 자체의 완성도는 확인할 수 없지만 제조한 실리콘은 이미 실용 수준인 것으로 나타났다.

EUV 리소그래피 양산 적용에 관해서는 최근까지 대만 파운드리 업체인 TSMC가 적극적으로 적용하여 7nm세대부터 적용할 것이라고 예상한 업계 관계자가 많았다. 그러나 2017년에 TSMC는 7nm세대에 대한 EUV 리소그래피 도입을 취소하고, ArF 액침 멀티 패터닝으로 7nm세대 반도체 양산을 시작했다. 현재는 EUV 리소그래피 양산 적용 스케줄을 확실히 갖고 있는 주요 반도체 업체는 삼성 뿐이다.

출처 - https://pc.watch.impress.co.jp/docs/column/semicon/1130163.html

'글로벌 IT 뉴스' 카테고리의 다른 글

| 인텔 10나노, 14나노 대비 2.7배 트랜지스터 밀도 향상 (0) | 2018.07.01 |

|---|---|

| Wi-Fi Alliance, 차세대 무선 보안 표준 WPA3 발표 (0) | 2018.07.01 |

| 마이크론, 96층 낸드플래시 및 1Ynm DRAM 출하 언급 (0) | 2018.06.23 |

| 구리 배선 미세화 과제를 위한 나노초 레이저 어닐 기술(nS Laser Anneal) (0) | 2018.06.23 |

| 인텔 CEO 브라이언 크르자니크, 사내 연예 발각으로 사퇴 (0) | 2018.06.23 |