AMD ZEN CPU 코어의 뉴럴 네트워크 (분기 예측 기능)

뉴럴 네트워크를 CPU 코어에 내장한 ZEN

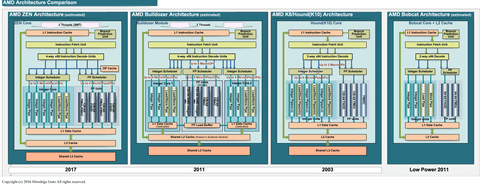

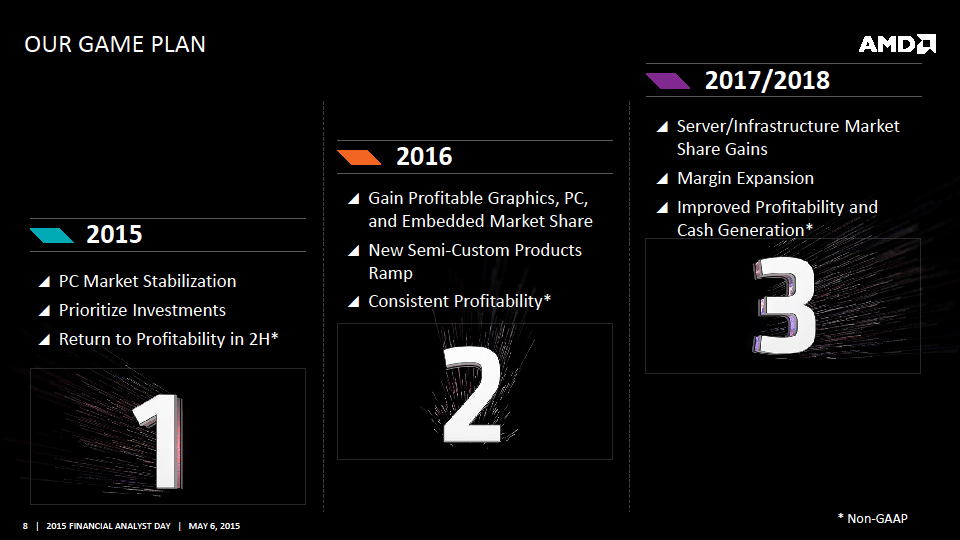

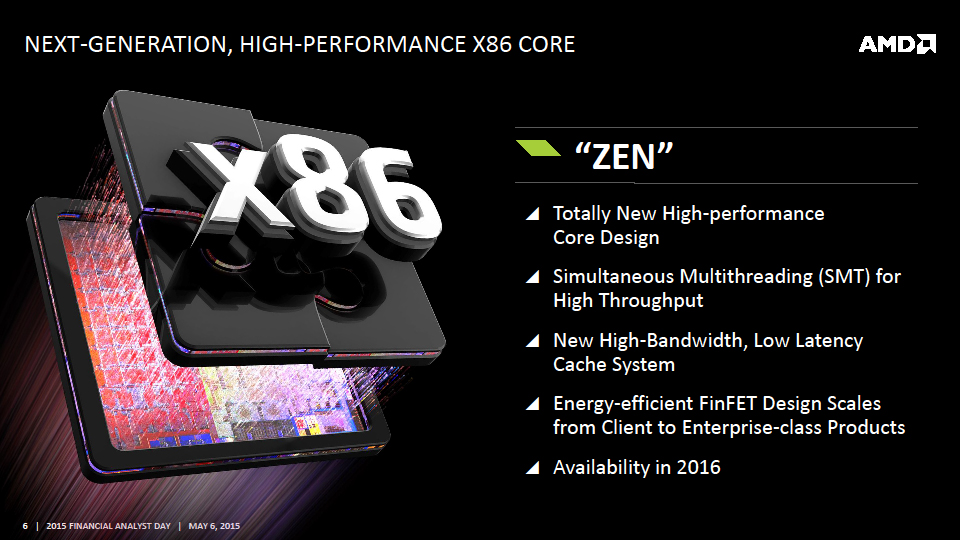

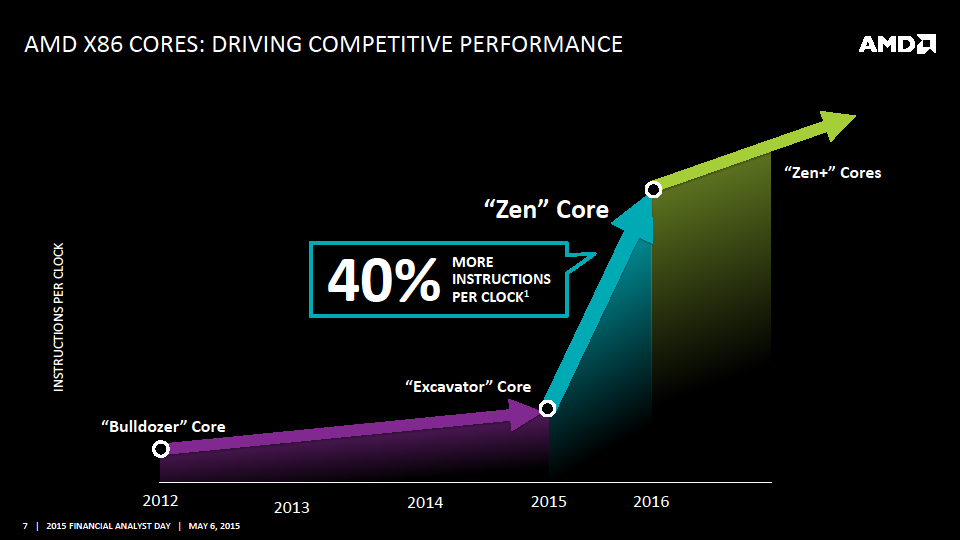

AMD는 2017년 1분기로 예정된 "ZEN" 마이크로 아키텍처 CPU 투입에 힘쓰고 있다. 제 1편으로 8코어의 고성능 데스크톱 CPU "Summit Ridge(서밋릿지)"는 새로운 브랜드 "Ryzen(라이젠)"으로 투입된다. AMD에게 6년만의 CPU 마이크로 아키텍처의 대대적인 쇄신이며 스레드 퍼포먼스에서 Intel CPU에 대항할 AMD에게 오랜만에 강력한 무기다.

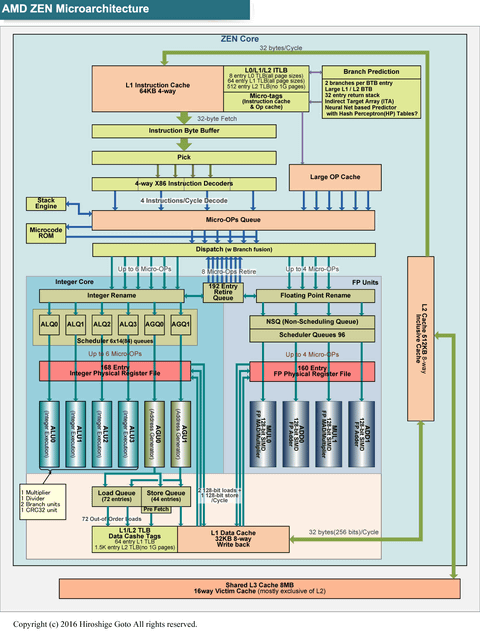

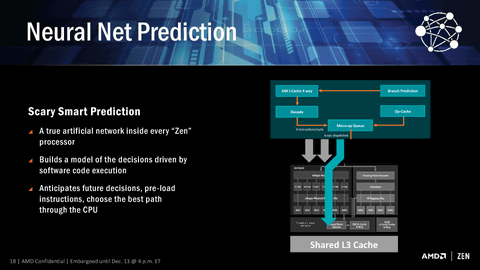

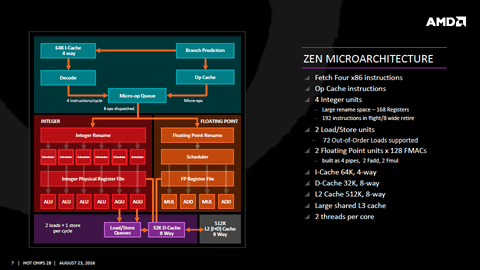

ZEN 마이크로 아키텍처는 Intel도 채용한 내부 명령(마이크로 OPs:Micro-OPs) 캐시 "OP캐시"등 고성능화와 저전력화에 큰 효과가 있는 기술을 도입한다. 또 Intel과 같이 SMT(Simultaneous Multithreading)도 도입한다. 그래서 AMD가 Intel 아키텍처의 이점을 도입한 것으로 보이지만 ZEN에는 아키텍처에서 실현한 다른 이점이 있다.

AMD는 단계적으로 ZEN 마이크로 아키텍처의 세부적인 내용을 밝히고 있다. 최근 AMD가 밝힌 마이크로 아키텍처의 큰 특징은 "뉴럴 네트워크(분기 예측 유닛)"이다. AMD는 ZEN의 분기 예측(Branch Prediction)에는 뉴럴 네트워크형 기술이 사용되어 분기 패턴을 학습하고 정밀도를 향상시킨다고 설명했다.

현재의 CPU는 파이프 라인화되어 프로그램의 연속된 명령을 파이프 라인상에서 실행한다. 문제는 조건 분기에서 조건이 판정된 분기 명령으로 분기되는지 여부를 결정한 단계에서 이미 10사이클 이상의 명령이 파이프 라인으로 흐르고 있다. 분기하지 않는다고 예상하고 분기 명령의 후속 명령을 실행하는 경우에는 파이프 라인상의 명령을 리프레시하고 분기의 첫 명령을 다시 시작해야 한다. 그 동안 CPU의 파이프 라인 처리는 정지가 발생하고 손실이 생긴다. 로스는 CPU을 공전시키고 성능을 떨어뜨릴 뿐 아니라 헛된 동작으로 소비 전력도 늘리게 된다.

여기에서 조건 분기 명령에 어떤 분기일지 예측하는 것으로 분기 손실을 줄이는 분기 예측이 필요하다. CPU 기사에서는 아웃 오브 오더(Out-of-Order) 실행과 투기 실행이 혼동되는 경우가 있지만 두 기술은 다르다.

분기 예측의 정확도가 높으면 CPU의 파이프 라인은 원활하게 동작을 계속할 수 있다. 그 만큼 성능이 올라가고 소비 전력이 떨어진다. 전력 효율이 생명인 현재의 CPU에 있어서 분기 예측은 가장 중요한 기술이다. CPU 설계에서 업체들이 가장 각축을 벌이고 있는 것이 분기 예측이라고 해도 좋을 정도다. x86 CPU의 경우는 명령 디코딩과 디코딩 후 명령 캐시 역시 중요하고 ZEN에서는 이 두가지의 개량이 큰 특징이다.

PlayStation 4(PS4)도 도입된 뉴럴 네트워크

ZEN 아키텍처에서는 분기 명령의 예측 알고리즘에 "뉴럴 네트워크"의 접근법을 사용하고 있는데 ZEN의 뉴럴 분기 예측은 최근의 뉴럴 네트워크 붐을 타고 구현된 것은 아니다. 뉴럴 네트워크 베이스의 분기 예측 자체는 새로운 기술이 아니기 때문이다.……특히 AMD에 있어서는.

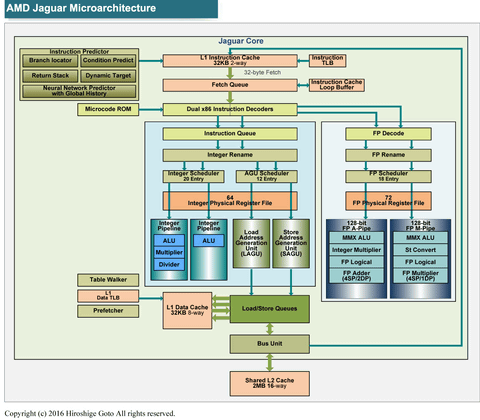

AMD는 이미 "Jaguar" 계열 CPU 코어에서 뉴럴 네트워크 베이스(퍼셉트론) 분기 예측을 채용하고 있기 때문이다. Jaguar는 Intel의 Atom에 해당하는 저전력 CPU 코어로서 저전력 APU(Accelerated Processing Unit)로 내장 게임기에 사용되고 있으며 Jaguar 코어의 PlayStation 4(PS4)는 뉴럴 네트워크(분기 예측)을 사용하고 있다.

ZEN의 뉴럴 네트워크는 이 회사의 저전력 CPU 코어에서 가져온 기술이다. PS4는 ZEN의 분기 예측 기술을 선점하고 있는 셈이다. 다만 AMD의 Bulldozer계 CPU 코어의 분기 예측 기술도 모두 포함되는 것은 아니며 Piledriver 세대에 뉴럴 네트워크가 도입됐을 가능성도 있다(그런 보도도 있다).

CPU의 분기 예측 기술은 CPU 제조 업체가 숨기고 싶은 기술이다. 분기 예측의 일반적인 테이블 크기 등은 밝히지만 구체적인 알고리즘에 대해서는 입을 다문다. 분기 예측 알고리즘은 CPU 마이크로 아키텍처의 차별화에 핵심이며 타사에 밝히고 싶지 않기 때문이다.

Jaguar의 뉴럴 네트워크 분기 예측에 대해서도 학회 등에서 Jaguar의 기술 발표때 공개되지 않았다. 그러나 AMD의 "APU 101:All about AMD Fusion Accelerated Processing Units" 등의 문서에서는 구석에 Series C와 Series E의 APU에는 뉴럴 네트워크 로직의 분기 예측(Neural Net Logic Branch Predictor)이 포함되어 있다고 적혀있다.

Samsung의 Galaxy S7도 뉴럴 네트워크 채용

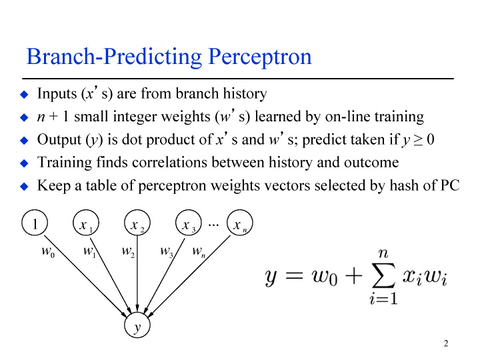

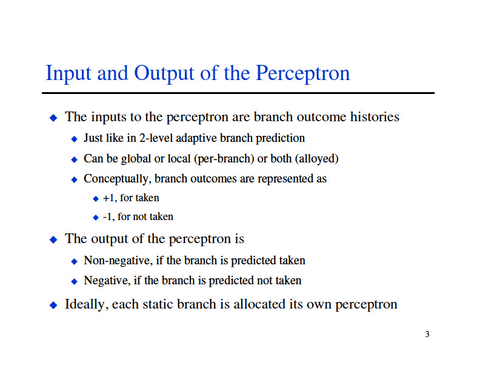

분기 예측에서 뉴럴 네트워크라고 해도 깊이가 있는 "CNN" 등을 사용하지 않고 가장 단순한 "퍼셉트론(Perceptron)"을 사용한다. 1999년에는 원형이 되는 아이디어가 논문으로 발표되고 있다. 2001년 논문 "Dynamic branch prediction with perceptrons"(Daniel A. Jimenez and Calvin Lin, the 7th International Symposium on High Performance Computer Architecture(HPCA-7), January 2001)에서 널리 알려지게 됐고 그 후로도 연구와 개량이 진행되고 있어 주목되는 예측 기술의 한가지다.

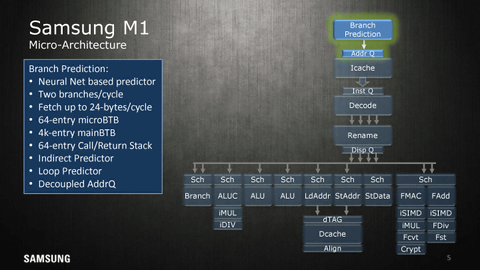

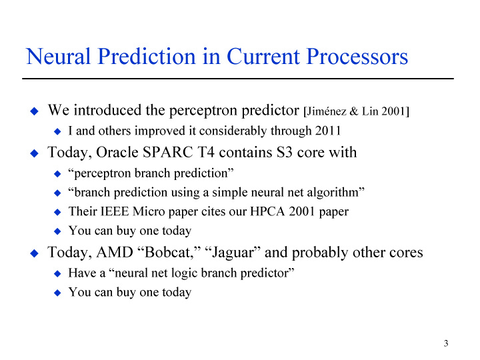

실제 프로세서에서도 AMD 외에 여러 제품에서 뉴럴 네트워크가 채용되고 있다. AMD의 저전력 CPU 코어인 Jaguar와 "Bobcat", 오라클의 "Oracle SPARC T4" S3 코어, 그리고 삼성의 "Exynos M1 Processor"다. M1은 Samsung의 SoC(System on a Chip) "Exynos 8890"에 탑재되어 삼성전자의 스마트폰 "Galaxy S7"등으로 쓰였다.

참고로 Bobcat과 M1의 주축인 아키텍트는 같은 Brad Burgess(현 VP, Chief CPU Architect Samsung Austin R&D Center(SARC)이므로 분기 예측이 비슷할 수밖에 없다. 또 Burgess는 Intel이 취소한 CPU "Tejas" 설계자이며 그 전에는 Motorola PowerPC 설계자였다.

뉴럴 네트워크는 위의 CPU 이외에도 채용되고 있을 가능성은 있다. 단, 분기 예측에 대해서는 각사가 비밀을 유지하기 때문에 알기 어렵다. Intel이 협력한 논문에도 여러명이 나왔으며 Intel도 열심히 연구하는 것으로 나타났다.

패턴 인식형 머신 러닝 문제인 조건 분기 예측

왜 분기 예측에서 뉴럴 네트워크인가, 그것은 원리적으로 궁합이 맞기 때문이다. 분기 예측 알고리즘은 가장 기본적인 2비트의 바이 모델(Bimodel) 분기 예측의 경우에 아래와 같은 스테이트에서 예측을 한다.

높은 가능성으로 분기하는 "Strongly taken"

낮은 가능성으로 분기하는 "Weakly taken"

낮은 가능성으로 분기하지 않는 "Weakly not taken"

높은 가능성으로 분기하지 않는 "Strongly not taken"

4가지 값의 스테이트 머신에서 분기가 성립되고 분기 예측 가능성이 높은 스테이트로 전이한다. 이 기본 바이 모델을 보면 뉴럴 네트워크(NN)의 가중치 변화에 의한 예측을 적용하는 생각을 할 수 있다. 실제 분기 예측 알고리즘에는 보다 다양한 패턴에 대응할 수 있는 2단계 맞춤형 분기 예측, 또 광역 분기 이력을 사용하는 글로벌 분기 예측, 그리고 거기서 발전한 "gshare"와 다양한 예측 기술이 발전, 결합되어 있다.

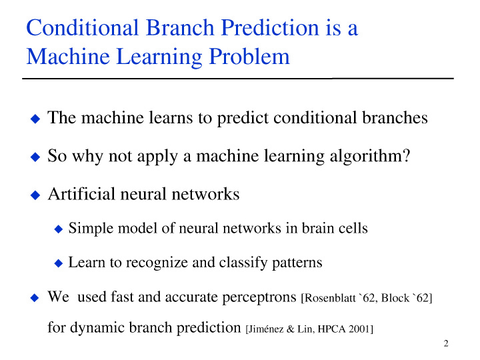

그러나 분기 예측이라는 것의 근원은 전형적인 머신 러닝 문제(Machine Learning Problem)라고 볼 수 있다. 분기 예측의 목적은 프로그램 스트림에서 조건 분기 명령이 분기하는 패턴을 해석하는 것이기 때문이다. 뉴럴 네트워크 분기 예측의 첫 논문 "Towards a High Performance Neural Branch Predictor"(Vintan, L. and Iridon, M., IJCNN, 1999)에서도 분기 예측은 패턴 인식 문제의 한가지라고 논하고 있다. 그렇다면 뉴럴 네트워크형 학습 알고리즘에서 분기 패턴을 인식하여 분류하면 예측 정밀도가 높아진다는 스토리다.간단히 말하면 뉴럴 네트워크에 의해 화상 중에서 패턴을 추출하고 인식한다면 분기 명령의 분기 패턴도 추출하고 예측할 수 있다는 것이다.

하드웨어 리소스가 커지면 예측 정밀도가 오른다

뉴럴 네트워크의 기본적인 아이디어는 1층 퍼셉트론(Perceptron)에서 분기 패턴을 학습하는 것이다. 가장 기본적 접근에서는 분기 이력으로부터 투입, 즉 과거의 분기 이력 각각에 온라인 학습 결과의 가중치(weight)를 달고 추론을 한다. 실제로는 뉴럴 네트워크 베이스의 분기 예측도 과거 10년 이상 동안 발전했으며 다양한 논문이 발표되고 있다.

뉴럴 네트워크에도 몇가지 문제점이 지적되고 있다. 자원의 증대와 레이턴시는 이 접근의 과제에서 이에 대해 개선하는 기법이 여럿 제안되고 있다. 뉴럴 네트워크 이력에 대해 가중치 데이터가 필요한 만큼 리소스를 먹게 된다. 또 학습(Training)은 이력이 길면 오래 걸린다.

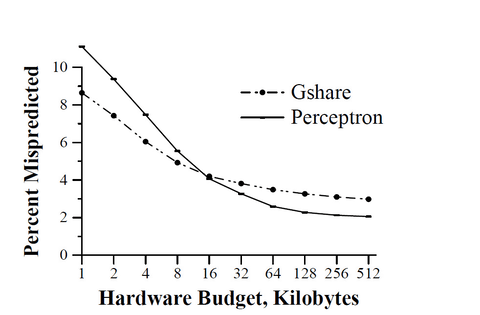

무엇보다 Jimenez는 뉴럴 네트워크의 이점은 이력의 길이에 따라서 밀도를 높일 수 있는 것이라고 밝혔다. 뉴럴 네트워크에서 필요한 리소스는 이력 사이즈에 대해 리니어로만 증가하지만 기존 접근 방식은 지수 함수적으로 필요한 자원이 늘어나기 때문이다. 그래서 뉴럴 네트워크가 일정 이상의 정밀도 향상에 대한 필요 자원이 상대적으로 적게 먹힌다고 한다. 하드웨어 자원의 증가로 일반적인 알고리즘인 Gshare와 Bi-Mode 보다 예측 정확도가 올라간다는 시뮬레이션 결과 등이 보고되고 있다.

위의 그래프는 같은 하드웨어 리소스량 안에서 예측 정밀도를 비교한 것이다. 분기 예측 유닛의 하드웨어 규모가 작을 경우에는 뉴럴 네트워크 베이스의 것이 쓸데없는 자원을 소모하고 정확도가 떨어진다. 그러나 자원의 규모가 커지면 상대적으로 예측 정밀도가 오른다는 구도다. 이러한 시뮬레이션대로라면 분기 예측 유닛의 규모가 커지면 뉴럴 네트워크 베이스의 것이 예측 정확도가 오르게 된다.

분기 이력 테이블을 길게 한 ZEN 아키텍처

AMD는 ZEN에 있어 종래의 고성능 CPU 코어보다 브랜치 히스토리 테이블(Branch History Table)의 크기를 2배로 했다고 설명했다. 뉴럴 네트워크 자원이 늘어나면 예측 정확도가 오를 수 있어 ZEN에서 기존의 분기 예측 알고리즘보다 예측 정확도가 향상되는 것을 기대할 수 있다.

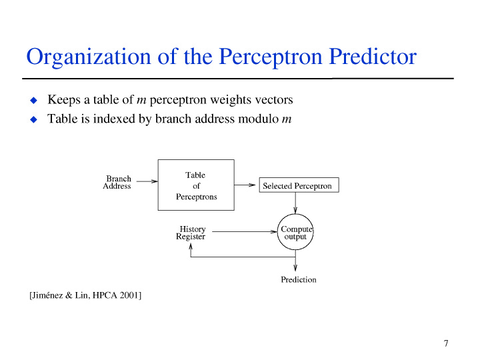

AMD의 뉴럴 네트워크 탑재의 세부적인 부분은 모른다. 하지만 보통의 분기 예측 테이블 외에 퍼셉트론의 가중치 데이터를 가진 버퍼를 갖는 것은 확실하며 이에 대해 AMD의 특허기술 "US20150121050 Bandwidth increase in branch prediction unit and level 1 instruction cache"가 있다.

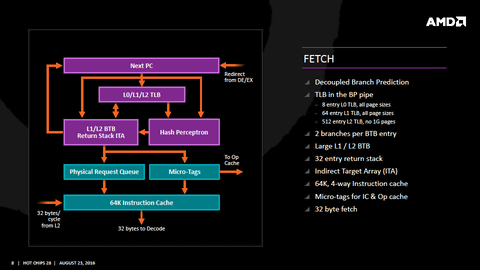

이 특허에서는 가중치 배열을 포함하는 테이블을 갖는 "Hash Perceptron(HP)"이 설명된다. 참고로 특허에서는 HP 자체도 L1과 L2의 2층 구조로 되어 있으며 ZEN이 탑재한 2수준의 뉴럴 네트워크가 될 가능성을 나타내고 있다.

ZEN의 분기 예측 유닛의 기본은 Jaguar와 흡사하다. 분기처의 예측 주소를 유지하는 "Branch Target Buffer(BTB)"는 L1명령 캐시와 밀접하게 통합되어 있다고 보인다. BTB는 1엔트리에 대해 2브랜치를 즉 2개 분기를 1사이클에 예측할 수 있다. BTB의 사이즈는 아직 밝혀지지 않았고 간접 분기에 대한 "ITA(Indirect Target Array)" 리턴 스택에 대한 32엔트리의 테이블도 갖는다.

참고로 ZEN은 실행 유닛군에 분기 유닛이 2유닛이다. 2개 분기 유닛은 SMT(Simultaneous Multithreading)에서 2쓰레드가 각각 분기를 실행하여 1스레드에서 2개 분기를 실행할 수도 있다. 후자의 1스레드에서 2분기의 경우는 아마도 선행하는 분기 명령의 예측이 분기하지 않는(not taken)경우와 같은 제약이 있을 가능성이 있다. ZEN의 경우는 1사이클 2분기 머신이기 때문에 분기 예측 정확도는 더 중요하다.

출처 - http://pc.watch.impress.co.jp/docs/column/kaigai/1036983.html

'글로벌 IT 뉴스' 카테고리의 다른 글

| 차기 아이폰용 유기 EL 디스플레이는 삼성 디스플레이가 독점 공급? (0) | 2017.01.02 |

|---|---|

| AMD 라이젠 프로세서는 인텔 i7 6900K 급 성능? (0) | 2017.01.02 |

| 안드로이드 탑재 노키아 Z2 Plus 긱벤치 스코어 등장 (0) | 2016.12.21 |

| 아이픽스잇, 무선 이어폰 "에어팟" 분해 리포트 공개 (0) | 2016.12.21 |

| 팀쿡 CEO, 우리는 멋진 데스크톱 Mac을 개발중이다 (0) | 2016.12.21 |