광대역 및 대용량으로 흔든 제 2세대 HBM2

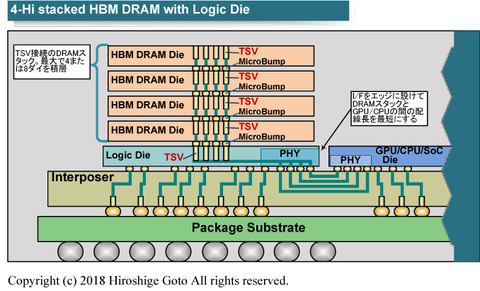

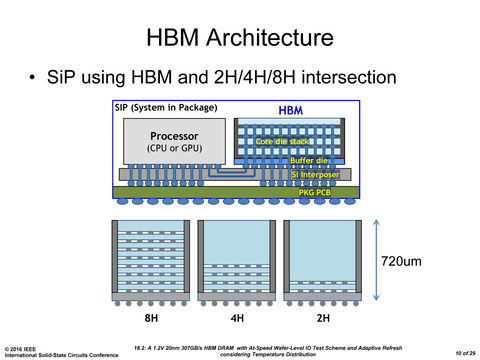

HBM2는 DRAM 자체가 고가에 기본 논리 다이도 필요하고 실장에 있어서는 CPU-GPU 사이의 배선에 인터포징이 필요하다. 그래서 칩 벤더에게 고비용 솔루션이 되고 있으며 결과적으로 채용할 수 있는 것은 고가 제품에만 한정되어 버렸다. NVIDIA를 예로 들면 HBM2는 하이엔드 컴퓨팅을 위한 GPU에 채용하며 그래픽용으로 설계한 GPU의 대부분에는 GDDR 시스템 메모리를 채용하고 있다.

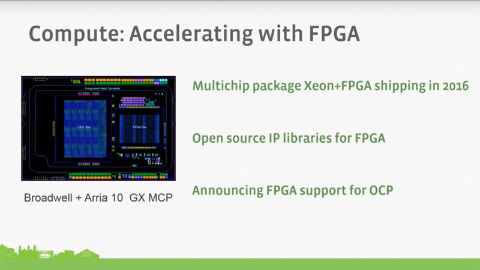

그러나 고비용에도 불구하고 HBM2는 수요가 점점 확대되고 있다. 그것은 딥-러닝(심층 학습)의 융성으로 GPU 등 액셀러레이터 류의 수요가 서버 측에서 높아졌기 때문이다. 결과적으로 서버용 GPU와 고성능 컴퓨팅(HPC)용 액셀러레이터/FPGA가 채용한 HBM2 메모리의 수요도 점점 확대됐다.

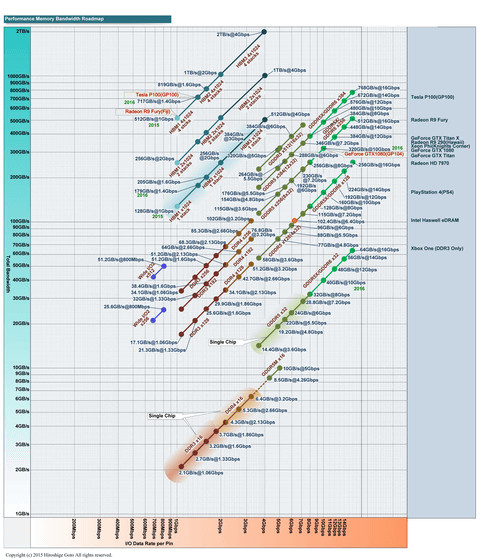

현재 HBM2는 DRAM 벤더에게 높은 가격에도 팔리는 고마운 상품이 됐다. 그리고 그 수요는 하이엔드 활용에 집중됐다. HBM2에 대한 현재의 시장 요구는 더 광대역, 그리고 더 큰 용량이다. 뉴럴 네트워크 베이스의 딥 러닝과 IoT(The Internet of Things) 등으로 가속되는 빅 데이터라는 요소가 있고, 메모리 대역으로 메모리 용량에 대한 압박은 갈수록 심화되고 있다.

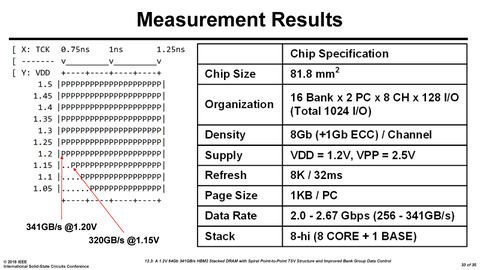

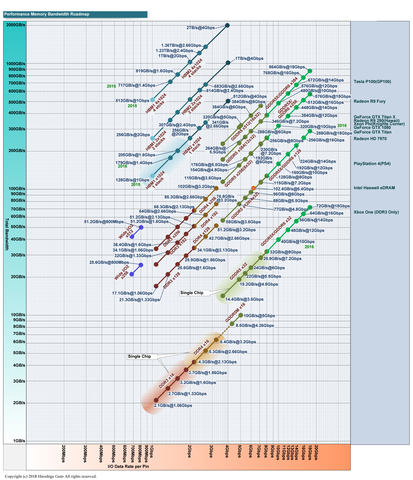

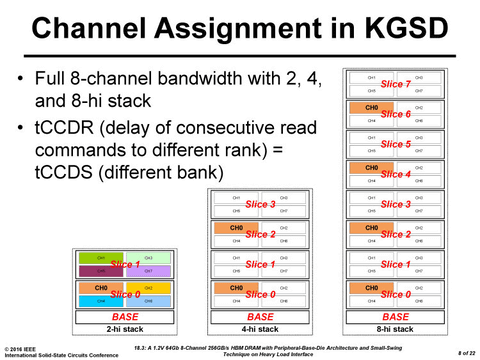

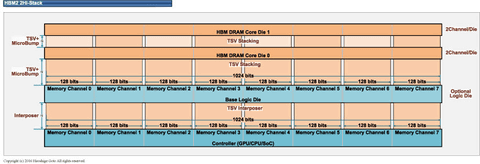

스택 DRAM의 니어 메모리는 1TB/s를 넘은 메모리 대역이 요구되고 있으며 메모리 용량도 가능하면 32GB가 달리는 흐름이다. SK hynix가 이번에 발표한 제 2세대 HBM2는 바로 그러한 수요에 부응한 아키텍처다. 데이터 전송 속도는 2.66Gbps까지 오르며 하이엔드 GPU(HBM2가 4스택) 메모리 대역은 1.36TB/s. 그리고 아마도 1TB/s 급 메모리 대역으로 32GB의 메모리 용량을 양립시킬 수 있다.

삼성도 제 2세대 HBM2 메모리 AquaBolt 발표

사실은 HBM2를 공급하는 또 하나인 삼성도 SK hynix와 마찬가지로 제 2세대 HBM2를 발표하고 있다. 이쪽은 아직 학계에서도 자세한 기술 발표는 없지만 "AquaBolt(아쿠아 볼트)"라는 코드네임으로 1월 공식 발표되고 있다. Samsung의 AquaBolt HBM2는 제품으로서 데이터 전송 속도를 2.4Gbps로 끌어올린다. 1스택당 메모리 대역은 307GB/s, 4개의 스택을 사용하는 하이엔드 GPU에서는 1.23TB/s의 메모리 대역이다.

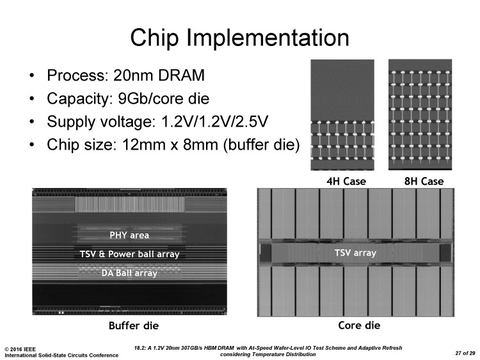

Samsung은 제 1세대 HBM2 "Flarebolt(플레어 볼트)"에서 보통 1.2V 구동에서는 1.6Gbps의 전송 속도로 제품화, 2Gbps는 1.35V 구동이라고 했다. 2016년 ISSCC에서 발표시("A 1.2V 20nm 307GB/s HBM DRAM with At-Speed Wafer-Level I/O Test Scheme and Adoptive Refresh Considering Temperature Distribution"K. Sohn, et al., ISSCC)은 2.4Gbps까지 가능했지만 제품이 어려웠다고 본다.

그러나 제 2세대 AquaBolt에서는 1.2V로 2.4Gbps를 달성할 수 있다는 것. Samsung의 제 2세대 HBM2의 목적도 SK hynix의 그것과 같은 선상에 있다. 그래서 Samsung의 AquaBolt HBM2도 4Hi/8Hi에 최적화 될 가능성이 있다.

흐지부지 된 소비자용 HBM

이러한 HBM2의 방향 전환은 실은 HBM2 세대에서만 머무르지 않는다. 향후의 스택도 DRAM 메모리 전체의 방향에 영향을 주고 있다. 구체적으로는 HBM 3세대 HBM도 어느 정도 비슷한 양상을 보이고 있다.

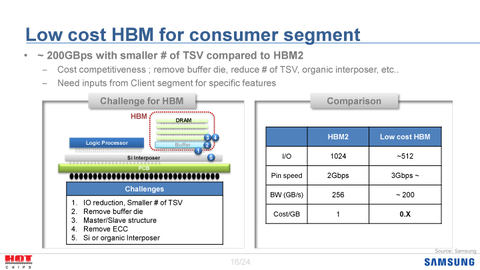

포스트 HBM2 에서는 당초 더 광대역화 된 규격과 가전 시장에 저비용으로 조명하는 규격의 2개 플랜이 나타나고 있었다. 후자의 가전용 HBM에서는 비용을 크게 낮추고, 비용이 문제가 되는 소비자 시장으로 침투할 계획이었다.

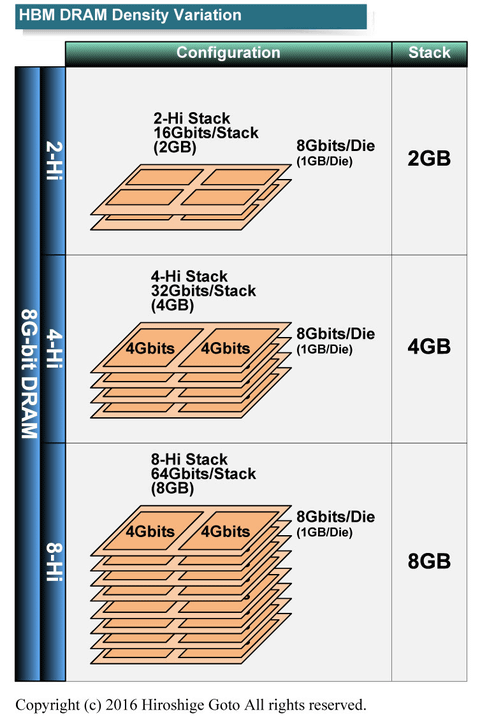

구체적으로는 염가 HBM은 인터페이스 버전을 HBM/HBM2의 절반인 512-bit으로 줄인다. I/O을 좁히고 다이 간 TSV도 줄인다. 또 HBM/HBM2 에서는 DRAM 다이군 아래에 베이스 로직 다이가 있지만 이것도 불 필요하게 한다. DRAM 다이 사이에 마스터/슬레이브 구성을 취하고, 현재의 HBM2 8GB 용량에 1GB의 ECC를 탑재하고 있지만 이것도 취소한다. HBM/HBM2)에서는 비싼 실리콘 인터포저를 필요로 하지만 가전용 HBM에서는 저비용 인터포저 등으로 가능하게 한다는 제안이었다.

그러나 이쪽의 가전 제품용 HBM 계획은 최소되어 현재는 검토되지 않는다. 한 JEDEC(반도체 표준화 단체) 관계자는 "DRAM 벤더는 규격의 분열을 싫어한다. 가전용으로 다른 하나의 DRAM을 만드는 것은 벤더 측에게 어렵다. 그래서 하나의 규격으로 통일하게 됐다" 고 밝힌다.

그러나 다른 업계 관계자는 배경에는 고객 측의 사정도 있다고 설명한다. "사실 가전용 HBM은 게임기로 채용을 상정하고 있었다. 막대한 대수의 게임기에 채용되면 시장이 쉽게 일어서기 때문이다. 하지만 게임기 벤더 측이 가전용 HBM의 채용을 꺼렸다. 그래서 규격 자체가 흐지부지됐다"

만약 가전용 HBM이 "PLAYSTATION 5(PS5)" 같은 차세대 게임기에 채용된다고 하면 제품화는 순조롭게 된다. 수천만 모듈의 HBM 수요가 한꺼번에 태어나기 때문이다. 반대로 말하면 그 만큼의 시장이 확실해지지 않으면 가전용 HBM은 만들기 어려운 상황이라는 것을 알 수 있다. 즉, 가전 시장에서 광대역 메모리 수요가 보이고 시장이 어느 정도 일어서지 않으면 메모리는 높은 가격으로 띈다. 하면 더욱 시장이 성장하기 어려워진다는 부정적인 악순환에 빠지게 되기 때문에 그것을 타파할 만한 고객을 확보하지 못하면 가전용 HBM은 어려울 것으로 보인다.

인텔 등이 이끄는 차세대 HBM

DRAM 벤더 측에게는 현재 HBM2는 고가에서도 잘 팔리고 있기 때문에 굳이 가전용 HBM에 주력할 필요가 적다는 사정도 있다. 딥 러닝(기계 학습)과 빅 데이터에 의한 하이엔드 시장에서 광대역 메모리의 수요 확대가 HBM2 수요를 견인하고 있다. 하이엔드 GPU 같은 고성능 엑셀러레이터에서는 HBM을 사용하는 것이 당연하게 되고 있다.

HBM계 DRAM은 원래 넓은 시장으로 침투하고 비용도 가격도 싸질 것으로 예상되고 있었다. 그러나 예상보다 고비용이기 때문에 침투는 한정되어 있었다. 그래서 시장이 좁아 고전한다고 여겨졌던 것이 초 광대역 메모리를 필요로 하는 시장 자체가 급격히 확대됐기 때문에 HBM2 메모리도 예상보다 급 성장하게 됐다.

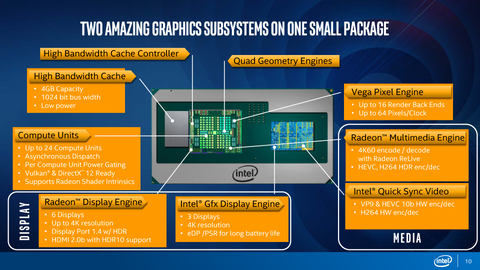

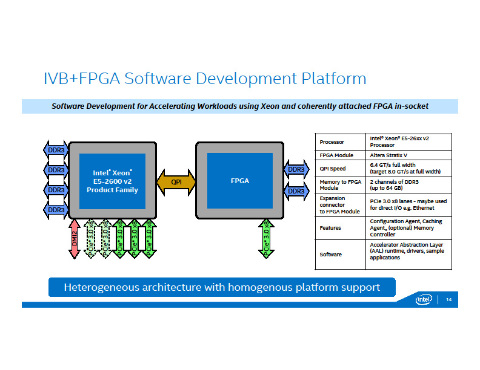

무엇보다 HBM3에 해당하는 차세대 HBM에서는 어느 정도 범위의 시장을 커버하는 것은 검토되고 있다. 초대 HBM은 사실상 AMD와 SK hynix에서 시작한 규격이다. 그러나 HBM2에서는 고객 측에서 이끄는 기업들이 엔비디아와 인텔로 바뀌었다. 그리고 차세대 HBM에서도 여전히 인텔이 점차 이끌고 있는 것으로 보인다. 인텔은 HBM2는 매우 열심히고, 자사 플랫폼에서 HBM2를 사용하기 위해 AMD GPU를 채용한 "Kaby Lake-G"를 개발했을 정도다.

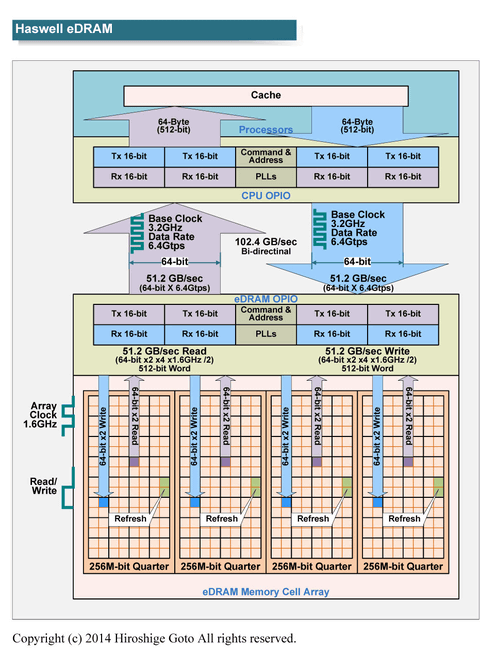

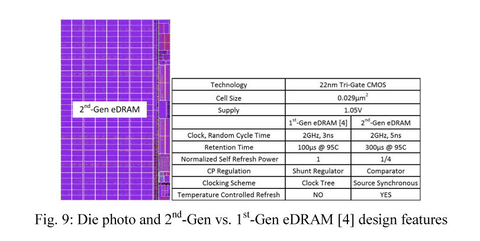

현재는 HBM3도 인텔이 줄줄이 요구 사양을 내걸고 DRAM 벤더 측이 그 사양에 응해 검토하겠다고 하는 흐름으로 나타나고 있다. 인텔은 최종적으로 PC에도 HBM 시스템 메모리를 채용하려 한다. 인텔은 자사 개발의 eDRAM 칩을 광대역 버퍼로 올린 CPU를 만들고 있다. 이 eDRAM을 HBM으로 바꾸는 것이 인텔의 목적 중 하나닫. 물론 하이엔드 액셀러레이터에서도 HBM의 채용을 확대할 것이라고 보인다.

인텔은 그 때문에 PC에서 HPC까지 범위를 위한 사양을 요구하고 있다고 추측된다. 그 중에는 사양대로 만들면 제조 비용적으로 어려워질 것과 기술적으로 고난도의 것도 포함된다고 한다. 그 때문에 차세대 HBM 사는 아직 흔들리고 있다.

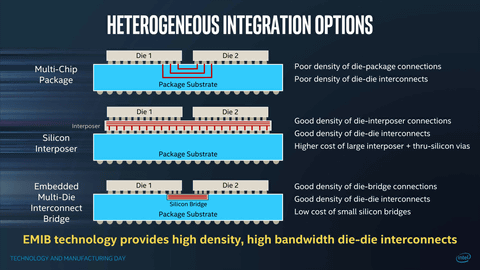

HBM2의 저비용화에서 인텔이 선두를 달려

광대역으로 가는 스택 DRAM, 그러면 저비용화는 어떻게 할 것인가. 이에 대해서는 복수의 솔루션이 나타나고 있다. 현재 HBM2에 대해서는 우선 비용이 높은 실리콘 인터포저보다 저비용 기술로 대체하는 수단이 개발되고 있다.

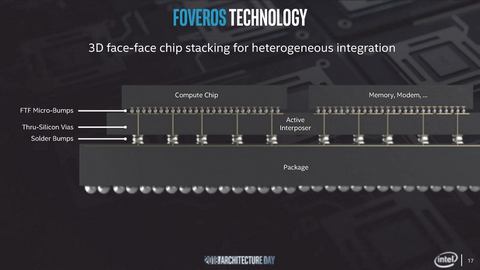

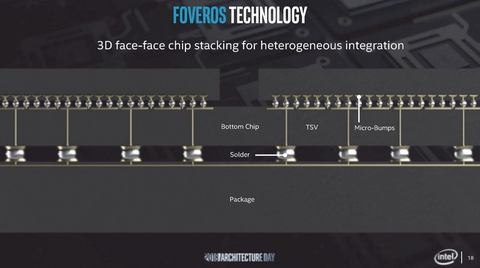

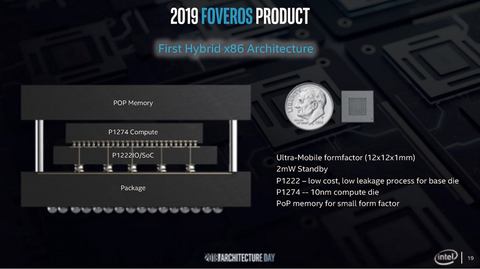

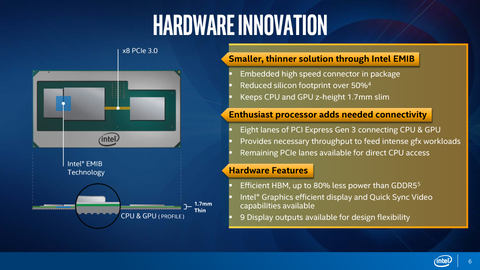

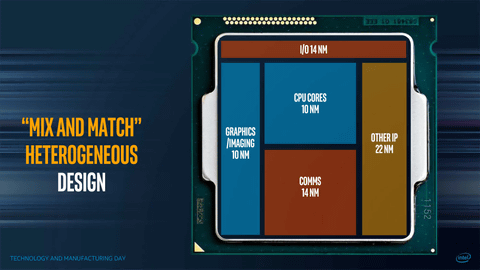

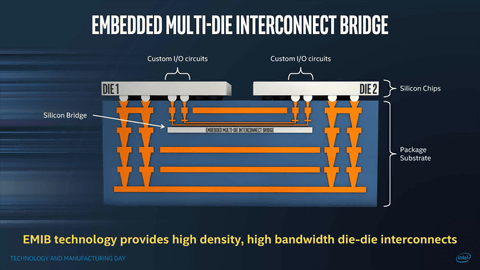

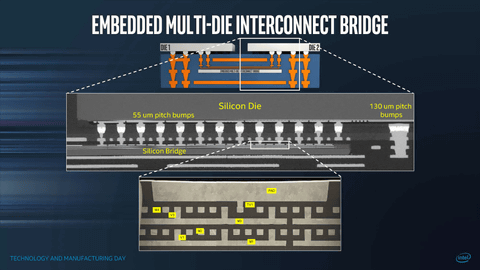

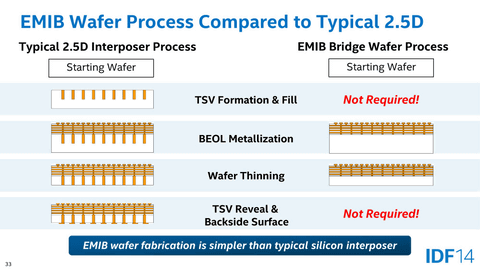

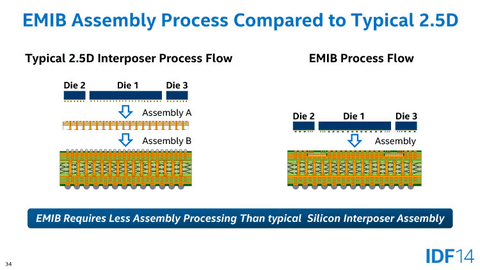

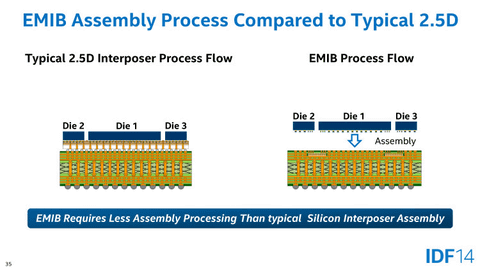

인텔은 8세대 Intel Core Processors with Radeon RX Vega M Graphic과 상표로 설정한 Kaby Lake-G에서 자체 개발한 패키지 기술 "Embedded Multi-die Interconnect Bridge(EMIB)"를 채용했다. 비용이 높은 실리콘 인터포저를 쓰지 않고 HBM2 메모리 접속을 가능하게 하는 2.5D통합 기술이다.

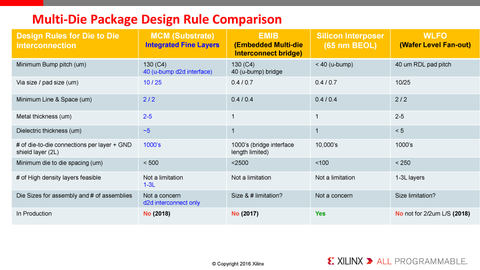

또 삼성은 지난해(2017년)의 Arm 기술 콘퍼런스 "ARM Techcon"에서 실리콘 이외의 재료 "Redistribution Layer(RDL)"에 의해 HBM 메모리를 서포트하는 플랜을 발표했다. 다만 RDL에서 지원에 어떤 제약이 생길 수 있다.

현재 HBM2는 DRAM 자체가 고가임이 문제라고 HBM에 주력하는 AMD의 Mark Papermaster(Chief Technology Officer and Senior Vice President, Technology and Engineering, AMD)가 설명한다. DRAM 자체의 가격은 HBM 계열 메모리 시장이 넓어져 볼륨이 늘고, 양산 효과가 안 나오면 해결이 어렵다. 스택 DRAM에서는 테스트 등의 비용도 높지만 이는 DRAM 자체의 기능으로 경감시킬 수 있다.

더 광범위한 보급에는 아직 과제가 많은 HBM 메모리지만 그 장래성을 의심하는 목소리는 적다. 그것은 프로세서의 성능 향상에 대해 충분한 메모리 대역을 제한된 전력 소비 범위 내에서 제공할 수 있는 기술이 현재 스택 DRAM 말고는 보이지 않기 때문이다.

이러한 상황으로부터 미래에는 메모리 스토리지 계층에서 워킹 메모리는 프로세서의 근처(동일 패키지 내)로 삼는 "니어 메모리(Near Memory)"와 확장 메모리 슬롯의 "파 메모리(Far Memory)"로 양분되는 방향으로 향할 것이 예상된다. DDR5와 비휘발성 메모리의 DIMM 류(NVDIMM, 3D Xpoint DIMM 등)도 중요하며 메모리는 향후 더욱 복잡해질 것으로 보인다.

출처 - https://pc.watch.impress.co.jp/docs/column/kaigai/1112395.html