차세대 DRAM(디램) 기술 (셀,셀렉터,채널,게이트,트랜지스터 등)

D램 미세화가 막혀 있다. 미세화를 막는 것은 메모리 셀의 셀렉터용 트랜지스터와 셀 캐패시터 양쪽이다. D램 메모리셀은 셀 셀렉터용 트랜지스터인 MOS FET과 전하 축적용 캐패시터로 구성된다. 메모리셀 면적을 가능한 작게 하기 위해서는 이전에는 미세화(가공치수의 축소)가 유력한 수단이었다. 그러나 2000년대 이후에는 미세화에 의존하는 비율이 점차 감소해 2010년대 들어 미세화에 크게 의존하지 않고 있다. 특히 2010년대 중반 미세 가공 기술 노드가 20nm 세대에 진입한 이후 미세화가 미세한 시각으로 접어들고 있다.

이 때문에 미세화(가공 치수의 축소) 이외의 기술적인 분석에 의해 D램의 기억밀도를 높이는 것이 일반적이다. 그리고 기술적인 분석에 대한 요구가 한층 더 강해지는 경향에 있다. 이 같은 사실이 국제학회 IEDM(미국 캘리포니아주 샌프란시스코에서 12월 15일 개최)에서 다시 불거졌다.

미세화의 한계를 상징했던 것은 주로 두 개의 강연이다. 하나는 12월 2일의 쇼트 코스(기술 강좌)에서 Samsung Electronics의 강연으로 D램 셀 기술의 트랜드를 과거부터 최신 상황까지 설명했다. 다른 하나는 12월 3일에 imec이 발표한 D램 셀 캐패시터의 연구 개발 성과다.(강연 번호 및 논문 번호는 2.7)

채널장을 확보하면서 트랜지스터를 작게 하다

D램 셀의 셀 셀렉터용 트랜지스터로 가공치수의 축소를 주로 막는 것은 채널장이다. D램의 성능(속도)을 유지하기 위해서는 셀 셀렉터 트랜지스터의 게이트(워드선)에 가해지는 전압을 가급적 낮추지 않으면 안된다. 예를 들어 현재도 게이트에는 약 3V로 최첨단 로직에 비하면 대폭 높은 전압을 인가하고 있다.

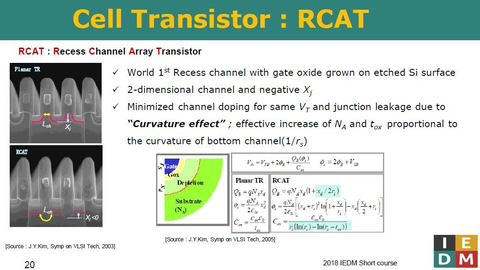

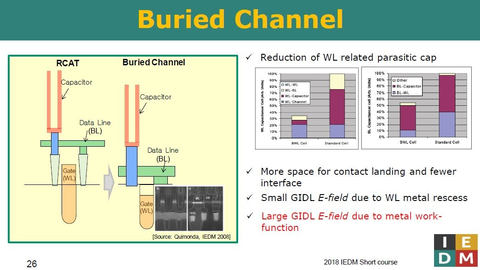

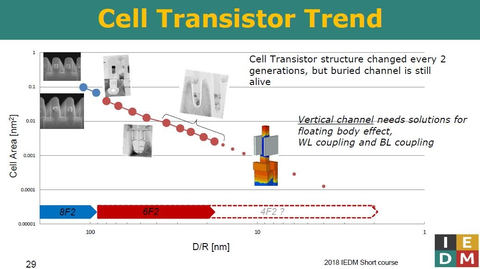

이 때문에 게이트장(실리콘 표면과 평행하는 방향: 횡방향 치수)을 짧게 해도 채널은 짧지 않다. 거기서 게이트를 채우고 채널의 형상을 직선에서 곡선으로 바꾸고 채널장을 확보하는 방법이 채택되어 왔다. 이 플래너형 트랜지스터로부터 매립 채널형 트랜지스터로의 구조 변화는 2000년대에 일어나 이후로는 매립 채널의 구조를 개량함으로써 연명을 도모해 왔다.

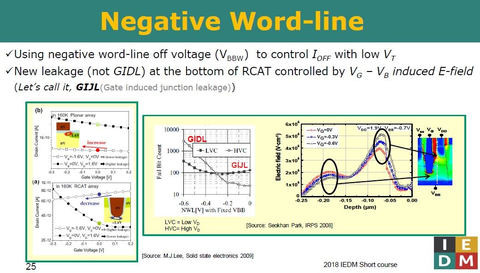

셀 셀렉터 트랜지스터에 있어서 또 하나의 큰 방향은 오프 상태에서 부전압의 인가다. 트랜지스터를 끄기 위해서 통상 게이트에 인가하는 전압은 제로 전압이다. 다만 미세화에 의해 트랜지스터의 이상한 전압이 내려오면 제로 전압에서도 리크 전류를 무시할 수 없게 된다.

거기서 오프 상태에서는 게이트에 부 전압을 인가하는 것으로 오프 전류를 작게 억제한다.

셀 어레이의 레이아웃을 변경하여 셀 면적을 축소

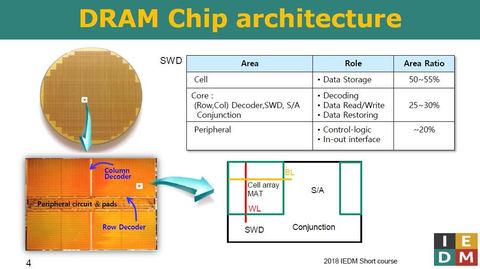

D램 메모리 셀의 고밀도화에 크게 공헌한 기술로 레이아웃 변경이 있다. 반도체 메모리의 연구 개발에서 메모리 셀의 크기를 나타내는 지표로서 "F2(F의 제곱)"가 잘 사용된다. 미세 가공의 기술 노드(설계 룰)를 나타내는 치수 "F(Feature size의 약칭)"에 대해 F의 제곱의 몇배의 크기(면적)로 메모리 셀을 실현할 수 있는지를 나타내는 것이다.

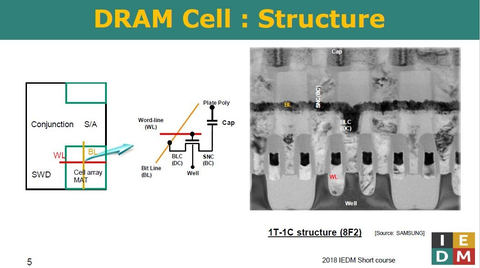

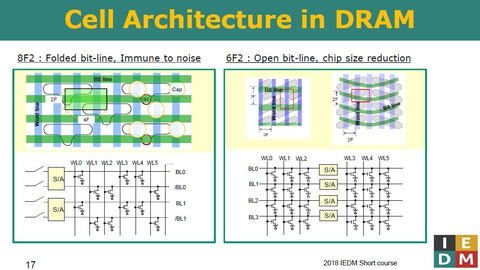

F2에 대한 비율(배수)이 작으면 같은 미세 가공 치수(설계 룰)에서도 메모리 셀이 작아진다. D램에서는 90nm 세대까지는 F2에 대한 배수가 8의 메모리셀을 채택해 왔다. "8 F2"라고 표기한다.

그것이 65nm 세대 이후 D램에서는 메모리 셀의 레이아웃을 변경함으로써 F2에 대한 배수를 6으로 축소하게 되었다. 단순 계산에서는 같은 가공 치수에서도 메모리 셀의 밀도가 1.33배로 향상된다.

조금 더 설명하면 "8 F2"세대에서는 레이아웃에 "반복 비트선(폴데드 비트선)"이라고 부르는 센스 앰프로부터 쌍이 되는 비트선(BL와/BL)을 평행으로 배치하는 아키텍처가 채용되어 왔다. 이 아키텍처에는 비트선 페어로 노이즈가 절감되는 강점이 있었다. 레이아웃의 효율보다는 노이즈 내성을 중시한 레이아웃이라고 할 수 있다.

그러나 65nm 세대 이후가 되면서 노이즈 내성보다 밀도 향상을 중시한 레이아웃 '오픈 비트선'이 채택되게 됐다. 오픈 비트선에서는 센스앰프의 좌우에 비트선을 붙인다. 메모리 셀을 보다 효율적으로 채울 수 있게 되어 결과적으로 F2의 배수는 "6"으로 감소했다. 현재도 D램 셀의 레이아웃은 이 6F2가 주류다.

차세대 D램은 크로스포인트 구조로 밀도를 1.5배 향상

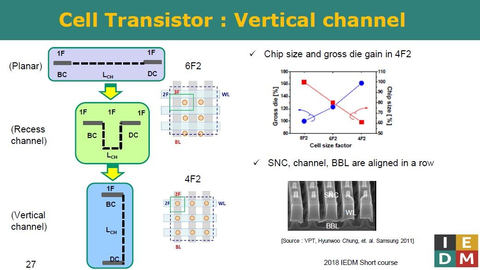

또 다음 수단으로 고안되고 있는 것이 셀 트랜지스터의 구조를 바꾸는 것이다. 채널을 수직방향으로 하는 셀 트랜지스터의 도입에 따라 셀 트랜지스터와 셀 캐패시터를 거의 완전히 겹쳐 레이아웃 한다. 그 동안 셀 커패시터는 셀 트랜지스터의 층과 접속하는 관계로 셀 트랜지스터에 대한 레이아웃이였다. 이것은 매립 채널 구조의 셀 트랜지스터에서도 변하지 않았고, 메모리 셀의 면적이 증가하고 있었다고도 할 수 있다.

그런데 채널을 수직 방향으로 레이아웃하면 트랜지스터와 캐패시터가 거의 완전히 겹친다. 원리적으로는 워드선과 비트선의 교차점에 캐패시터를 배치할 수 있게 된다. 즉 크로스 포인트 구조다. 그러면 전술한 F2의 배수가 "4"로 줄어든다. 즉 원리적으로는 "4 F2"의 메모리 셀 면적이 되고, 메모리 셀 어레이의 밀도가 1.5배로 향상된다. 극단적으로 보면 이것만으로 16Gbit의 D램이 24Gbit의 D램이 된다. 이 차이는 크다.

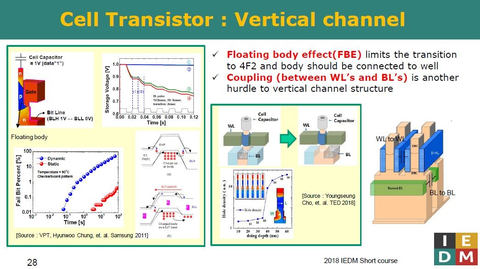

물론 과제는 있다. 바디가 전기적으로는 부유 상태(불안정)가 되는 것, 인접하는 워드선의 결합이 강해지는 것, 인접하는 비트선의 결합이 강해지는 것이라는 문제가 우려된다.

캐패시터의 정전 용량이 서서히 저하

여기까지는 주로 셀 트랜지스터와 셀 레이아웃에 대해 기술해 왔다. 잊지 말아야 할 것이 셀 커패시터다.

셀 캐패시터는 신호 전하를 축적하는 중요한 역할을 담당한다. 기본 성능은 2가지로 정전용량과 리크전류다. 정전용량은 가능한 한 크게 한다. 신호대 잡음비를 벌기 위해서다. 리크 전류에는 최대 허용치가 있다. 허용치를 초과하면 데이터를 유지하는 시간이 짧아져 제품 사양에 있어 재충전 주기가 짧아진다. 바꿔 말하면 대기시 소비 전력이 증가한다.

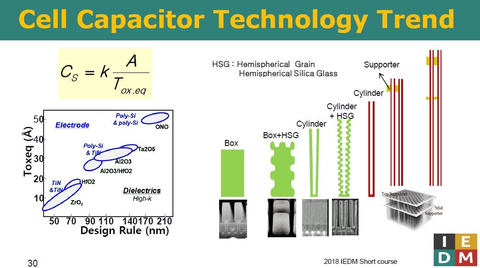

정전 용량은 캐패시터 절연막의 비유 전율과 캐패시터 전극의 면적에 비례해 절연막의 막후에 반비례한다. 미세화에 의해서 설계 룰을 축소하면 캐패시터 전극의 면적이 감소한다. 즉 정전 용량이 저하된다. 정전 용량의 저하를 막기 위해 주로 2개의 수단이 채용되어 왔다.

하나는 절연막의 재료를 비유전율이 높은 재료(고유전율 재료)로 변경하는 것이다. 설계 룰이 200nm 이후 절연막의 재료는 비유전율보다 높은 재료로 몇 번이나 변경되어 왔다. 현행 세대의 D램 캐패시터로 잘 알려져 있는 절연막은 "ZAZ"라고 부르는 산화 지르코늄(ZrO2)과 아르미나(Al2O3), 산화 지르코늄(ZrO2)의 3층막이다.

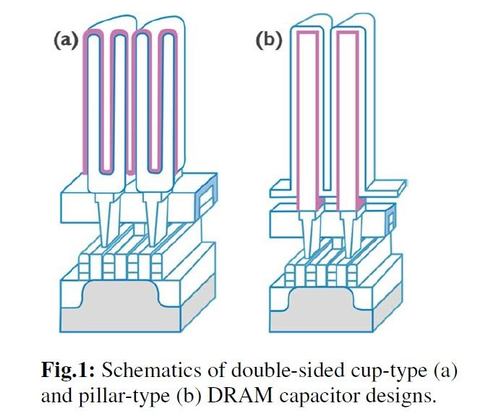

다른 하나는 캐패시터 전극의 형상을 수직으로 펴거나 캐패시터 전극의 표면을 곡선으로 변경하거나 하는 것으로 전극의 면적을 버는 것이다. 캐패시터 전극의 형상은 실린더 혹은 컵처럼 되어 한층 더 높게(길게) 되어 왔다.

。

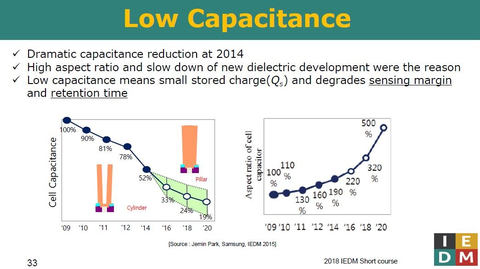

그럼에도 불구하고 실제로는 2012년을 경계로 이후 캐패시터의 정전 용량이 꽤 급격하게 저하됐다. 그 때까지도 정전용량은 내려가고 있었지만 그 경향은 비교적 느슨했다. 그러나 새로운 고유전율 재료가 발견되지 않은 것과 캐패시터 전극의 높이를 올리는 비율이 무뎌져 온 것이 정전 용량을 급속히 낮추는 결과가 되고 있다.

고유전률 재료의 캐패시터로 1x세대의 D램에 대응

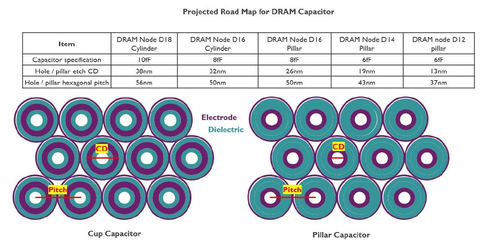

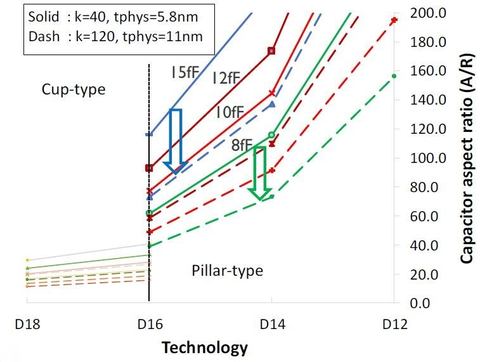

캐패시터 전극의 형상에는 주로 실린더(컵)형과 필라(원주)형이 있다. 같은 높이에서 전극의 면적을 크게 확보할 수 있는 것은 실린더형인데 형상이 복잡하기 때문에 절연막의 품질에 대한 요구가 높은 것이 약점으로 지적된다. 절연막의 리크 전류가 문제가 되기 쉽다.

이것에 대해 필러형은 형상은 단순하게 되지만 아스펙트비를 높게 해야 하기 때문에 에칭이나 성막 등의 부문에서 과제가 있다. 여기서 필러의 형성을 2단계로 나누는 것에 의해 아스펙트비의 문제를 완화하는 것이 고안 되어 왔다.

이번 IEDM에서는 필러형 셀 캐패시터의 아스펙트 비율을 완화하는 기술로서 imec가 종래보다 비유전율이 높은 새로운 고유전재에 의한 셀 캐패시터를 제안해 왔다. 재료는 티탄산 스트론튬(SrTiO3) 절연 재료와 루테늄(Ru) 전극 편성이다.

이 조합에 의해 금속/절연막/금속(MIM) 캐패시터를 개발한 결과 티탄산 스트론튬 막후가 11 nm 때에 118로 지극히 높은 비유전율을 얻을 수 있었다. 산화막 환산의 막후는 0.4 nm. 리크 전류는 0.1μA/평방 cm로 상당히 낮다.

imec는 또한 D램의 기술 노드와 셀 캐패시터의 로드맵을 공개했다. 18nm세대는 실린더(컵)형의 캐패시터를 사용한다. 16nm세대에서는 실린더형과 필러형 양쪽이 있으며 같은 정전용량에 대해 필러형은 가공치수가 짧아져 아스펙트비가 높아진다. 14nm세대와 12nm세대에서는 필러형의 캐패시터로 정전용량의 저하를 최대한 억제한다. 18nm 세대에서는 10fF인데 반해 16nm 세대에서는 8fF, 14/12nm 세대에서는 6fF라는 시나리오다.

기억용량 확대폭이 2배에서 1.5배로 줄어들 가능성

D램 대기업 벤더에 의한 기술노드는 1Xnm세대가 양산중이며 1Ynm세대가 양산시작중, 1Z세대가 개발중인 상황이다. 구체적으로 1Xnm세는 18nm세대, 1Ynm세대는 17nm세대, 1Znm세대와는 16nm세대.

1Znm세대의 뒤는 1알파nm세대, 그 다음이 1베타 nm세대라는 것이 현재의 명칭이다. 1Znm세대까지의 조각이 그대로 이어진다고 가정하면 1β세대란 14nm세대인 셈이다. 4세대에서 4nm밖에 안 된다는 것은 과거 D램 개발에서는 상상할 수 없었던 일이다.

이러한 사실로부터 이해할 수 있는 것은 D램의 실리콘 다이당 대폭적인 대용량화를 성립시키는 주요한 수단은 미세화 이외의 기술적인 고안에 의하는 것이다. 그 수단이 버티컬 구조의 트랜지스터나 비유전율이 111인 초 고유전율 절연막을 사용하는 캐패시터가 될지는 알 수 없지만 요소 기술이 이미 존재하고 있다는 사실이 중요하다. 이들 요소 기술을 제품 수준으로 높이면 D램의 대용량화를 계속할 수 있기 때문이다.

가능성이 적지 않은 것은 기억용량 확대 폭이 앞으로 점점 줄어들 것이라는 시나리오다. 1990년대까지는 세대별로 4배였던 기억용량의 확대폭은 2000년대 이후로는 세대별로 2배가 되었다. 1Gbit의 다음은 2Gbit, 그 다음은 4Gbit이 되었고, 다음으로 8Gbit, 그리고 16Gbit로 기억용량이 확대되어 왔다.

16Gbit 에서는 2배라고 할 수 없다. 16Gbit의 다음은 32Gbit가 아니라 24Gbit가 될 가능성이 있다. D램 실리콘 다이 면적은 약 60m 이하라는 것이 하나의 기준(제조원가로는 2달러 이하라는 뜻)이므로 이 제한을 유지한다는 전제라면 기억용량의 대폭 확대는 기대하기 어렵고, 당분간은 이러한 것에 유의하면서 방향을 지켜보고 싶다.

출처 - https://pc.watch.impress.co.jp/docs/column/semicon/1156988.html

'글로벌 IT 뉴스' 카테고리의 다른 글

| 인텔, 업계 최초의 로직 3D 적층 패키징 기술 Foveros 발표 (0) | 2018.12.15 |

|---|---|

| Intel Architecture Day) 인텔의 차세대 아키텍처 기술 방향 (0) | 2018.12.15 |

| ASUS, USB Type-C 게임 헤드셋 ROG Delta 발매 (0) | 2018.12.09 |

| QNAP, 10GBASE-T 가정용 나스 HS-453DX 발표 (0) | 2018.12.09 |

| 구글의 콘텐츠는 어떻게 사용자에게 전달되는가? (0) | 2018.12.09 |