아이폰6s A9칩은 이례적인 멀티-파운드리 제조

현재로는 드물게 2개의 파운드리에서 제조

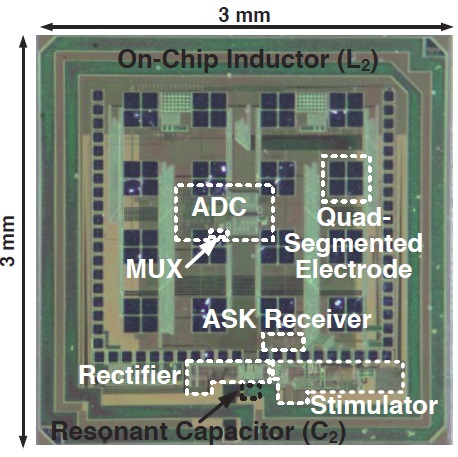

아이폰6s/6s 플러스 칩이 2개의 다른 파운드리에서 제조되고 있는 것이 화제다. 아이폰6s/6s 플러스의 핵심 SoC(System on a Chip)인 "Apple A9"은 애플의 발표대로 새 트랜지스터 아키텍처인 FinFET 3D트랜지스터 기반이었다. 놀랍게도 지금까지의 Apple A시리즈 SoC와 달리 제조는 하나의 파운드리가 아니라 두군데의 파운드리에 2개의 프로세스 기술에 걸친 것 같다. 삼성의 14nm 공정과 TSMC의 16nm 공정이다.

왜 2종류의 프로세스로 생산된 A9이 있는 것이 그렇게 놀라운 것일까. 그것은 현재의 첨단 프로세스 기술에서 고성능 SoC의 경우 2가지 소스를 위한 설계에는 막대한 비용과 노력이 필요하기 때문이다. A9 같은 복잡하고 성능과 전력 비용(PPA:Performance, Power, Area)의 튜닝이 요구되는 칩의 경우에는 시간이 걸린다. 물론 반도체 제조에 필요한 마스크의 비용도 배가 된다.

그래도 한 프로세스의 제조를 시작하고 뒤늦게 다른 프로세스의 제조를 시작하는 케이스는 있다. A제품용 A칩을 한 프로세스에서 제조하고 B제품용 A칩은 다른 프로세스를 쓴다는 식의 패턴이다. 그러나 발매시 제품에 2종류의 파운드리에서 설계의 칩을 투입하는 것은 매우 이례적이다. 2개의 다른 프로세스에 최적화 된 물리 설계를 병행해야 하기 때문이다. 그런 일반적이지 않은 것을 이번에 Apple 하고 있는 것 같다.

제조상의 문제를 시사하는 2파운드리 전략

이 사건이 시사하는 것은 Apple이 하나의 파운드리 생산 라인에서는 아이폰6s/6s 플러스의 출시에 필요한 A9칩 수량을 확보하지 못한 것이다. 혹은 확보하지 못할 우려가 있어 그 때문에 비용을 들이고도 보험을 들 필요가 있었는지도 모른다. 아이폰6s/6s 플러스의 판매는 첫 주말에만 1,000만대라 그것은 당연할지도 모른다. 그러나 20nm공정의 A8에서는 TSMC 하나에 의존한 것을 생각하면 이번은 이례적이다.

출시때 두 파운드리의 칩이 탑재된다는 점에서 이 결정은 오래 전, 아마 1년 이상 전에 이루어진 것으로 보인다. 그래서 A9의 제조를 삼성과 TSMC가 모두 담당한다는 소문이 나돌았다고 본다. 2소스가 바람직하다는 정도의 이유로 A9을 두 군데의 파운드리로 분산하는 것은 생각하기 어렵기 때문에 어떤 다급한 이유가 있었음은 확실하다.

만약 Apple이 칩의 생산 수량 확보 때문에 A9를 삼성과 TSMC에 분산한 것이라면 그것은 FinFET 프로세스의 초기 양산 볼륨이 상당히 한정되어 있음을 뜻한다. 혹은 유연한 시작에 문제가 있을수도 있다.

또 Apple이 TSMC에도 제조를 위탁한 것은 TSMC의 FinFET 프로세스를 사용, Apple이외의 고객의 제조 라인의 능력을 압박하고 있는 것을 의미한다. 즉, 아이폰6s/6s 플러스 이외에는 FinFET 프로세스에서 생산량에 제약이 생길 가능성이 있다. TSMC의 FinFET 프로세스는 고객의 칩 업체 수가 많아 영향이 크다.

물론 삼성과 TSMC의 FinFET 프로세스의 양산 태세가 갖추어지면서 FinFET 프로세스에서 웨이퍼 출하량이 늘고 생산량의 문제는 해결된다. 그러나 초기에는 Apple이 제조 능력의 상당 부분을 차지하는 것으로 보인다.

참고로 삼성은 대형 파운드리의 다른 한쪽인 GLOBALFOUNDRIES와 14nm공정에서 제휴하고 있다. 삼성과 GLOBALFOUNDRIES는 14nm공정을 레시피 차원에서 호환되어 삼성에서 제조하는 A9은 거의 그대로 GLOBALFOUNDRIES에 제조를 옮길 수 있다. 그래서 내년(2016년)에는 Apple은 A9을 3소스로 제조 위탁할 수 있게 된다.

동일 칩 제조에서 명백히 드러난 삼성/GF FinFET 프로세스의 스케일링

2파운드리의 A9 발단의 하나는 아이폰6s/6s 플러스의 분해를 실시한 칩 분석 기업 chipsorks의 테크 블로그에서 TSMC 버전과 삼성 버전의 존재가 지적된 것이다. TSMC와 삼성은 파운드리 중에서 현재 FinFET 프로세스를 양산할 수 있는 2대 기업이다. 삼성은 "14nm", TSMC는 "16nm"의 프로세스 노드 이름으로 FinFET 프로세스를 제공하고 있다.

이 "14"와 "16" 등의 프로세스 노드 숫자는 실체가 있는 숫자가 아니라 상대적인 지표로 붙여진 제품 번호 같은 것이다. TSMC 16nm과 삼성 14nm는 모두 배선층 배선 간의 거리인 메탈 피치(Metal Pitch)는 전 세대의 20nm 공정과 같은 64nm(M1)피치를 채택하고 있다. 인텔의 14nm 공정 같은 52nm라는 좁은 메탈 피치의 프로세스가 아니라는 것.

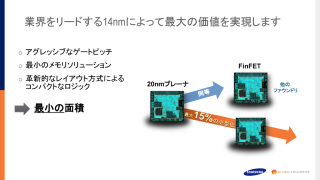

다만 까다롭기는 삼성측의 프로세스는 게이트 간 간격으로 게이트 피치(Gate Pitch)가 TSMC의 표준보다 좁다. 그래서 같은 칩을 레이아웃 한다면 삼성 프로세스의 다이가 작아진다.

실제로 chipworks의 분석 블로그를 보면 A9에 대해서도 삼성 버전은 96㎟인 반면 TSMC 버전은 104.5㎟로 리포트하고 있다. 삼성이 8% 정도 다이가 축소되고 있다. 삼성, GLOBALFOUNDRIES 그룹의 14nm공정은 TSMC의 16nm에 비해 최대 14~15%의 다이 축소가 된다고 설명하고 있었다. 거기까지의 비율은 아니지만 삼성 프로세스 스케일링의 우위성이 동일한 칩을 제조하기에 증명된 것이다. 현재의 첨단 모바일 SoC 다이 사이즈로는 어느 쪽도 적당한 라인이다.

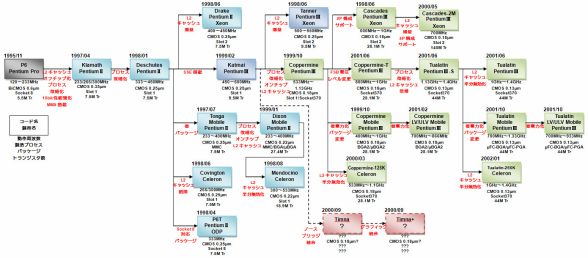

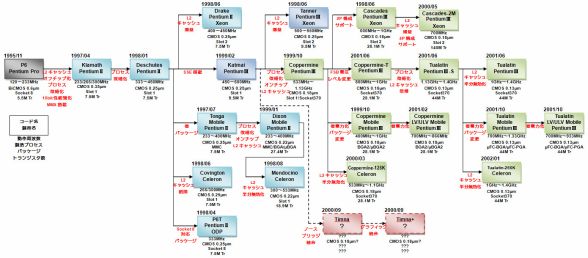

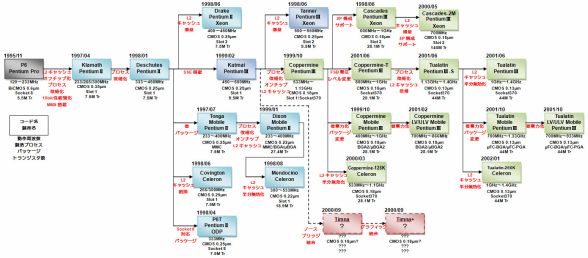

프로세스의 차이는 당연히 성능/소비 전력에도 영향을 미치지만 이번에는 아직 거기까지 보이지 않는다. 다만 두 프로세스 모두 FinFET이라 누설 전류(Leakage)는 종전 프로세스보다 대폭 개선된다. 참고로 지금까지의 Apple A시리즈의 제조 프로세스는 삼성의 45nm(A4/A5)→ 32nm(A6)→ 28nm(A7), TSMC의 20nm(A8), 그리고 이번 삼성 14nm/TSMC 16nm(A9)으로 바뀌고 있다.

LPDDR4 2GB로 용량과 동시에 메모리를 확장

칩상의 아이폰6s 계열 확장의 하나는 DRAM이다. 이 세대에서 Apple은 지금까지 LPDDR3에서 LPDDR4로 이행했다. 또, 메모리양도 아이폰 6세대까지의 1GB에서 2GB로 증량되어 Android계 최첨단 단말기 수준의 메모리로 겨우 올라왔다. 그리고 이것은 Wide I/O 시스템 메모리가 전진에 실패했음을 상징한다.

아이폰6s/6s 플러스가 Wide I/O2를 사용하지 않는 것은 Wide I/O2의 생산이 움직이기 시작하지 않았기 때문에 자명한 것이었다. Wide I/O2는 모바일 기기용의 스택 DRAM기술로 LPDDR4보다 이 메모리 대역에서 저전력이다. 그러나 제조 비용이 올라간다.

Wide I/O2 같은 새로운 메모리는 시작했을때 큰 고객이 필요하다. 대량으로 쓰는 고객이 붙어 양산이 빨라지면 가격도 낮출 수 있다. 가격이 떨어지면 고객도 늘어난다. 그러나 처음에 거대한 고객이 없어 양산 효과에 의한 비용 절감을 기대할 수 없기 때문에 메모리가 언제까지 계속 지나도 보급할 수 없는 네거티브 악순환에 빠진다.

Wide I/O 시스템 메모리는 분명히 목표는 Apple이지만 Apple은 메모리에 대해서는 매우 보수적이고, 신기술에는 뛰어들지 않는다. LPDDR4도 아이폰6s/6s 플러스 세대에서 채용한 것은 생산량과 가격 문제일 것이다.

이번에는 저전력에 이점이 있는 FinFET 프로세스의 SoC와 대역당 전력 소비를 줄이는 LPDDR4가 아이폰6s세대에 갖추어진 셈이다.

출처 - http://pc.watch.impress.co.jp/docs/column/kaigai/20151001_723559.html

'글로벌 IT 뉴스' 카테고리의 다른 글

| NVDIMM, 비휘발성 메모리를 DIMM에 장착하는 표준 규격 (0) | 2015.10.08 |

|---|---|

| 24Gbps 차세대 직렬 스카시 사스4 개요(SCSI SAS-4) (0) | 2015.10.08 |

| MIT, 투명 유리를 조형할 수 있는 3D프린터 개발 (0) | 2015.09.20 |

| MSI 초소형 베어본 큐비(Cubi) 시리즈 발매 예정 (0) | 2015.09.20 |

| 퓨처마크, 가상현실(VR) 벤치마크SW "VRMark" 발표 (0) | 2015.09.16 |