인텔, 알테라의 FPGA "Arria 10 GX"를 통합한 Xeon 발표

지난 3월 9월~10일(현지 시간) 미국 새너제이에서 열린 Open Compute Project US Summit 2016에서 인텔이 흥미로운 신제품 2가지를 선보였다.

첫번째는 Broadwell을 기반으로 한 16코어/32스레드 "Xeon D-1581". 지금까지 Xeon D는 8코어였기 때문에 코어 수가 배가 된다. 강연 설명에서는 페이스북의 협업으로 16코어와 Ethernet 내장을 실현하는 다이를 공개했지만 크기를 보면 8코어 제품과 큰 차이는 없고 새로운 다이인지는 불명.

만일 새 다이인 경우 Broadwell-EP와는 다른 계통의 다중 코어 구성 다이로 그 경우 링 버스의 구조 등 약간 의문점이 남는다. 또 다이가 가짜일 가능성도 있고 8코어 ×2의 Multi-Chip Package(MCP)구성 가능성도 남아 있다.

이 Xeon D-1581은 1.9GHz로 구동하고,(다만 Ark의 정보로는 베이스 1.8GHz, Turbo시 2.4GHz 구동으로 알려졌다) 캐시는 24MB, TDP는 65W. 대응 메모리 채널 수는 듀얼채널 DDR4와 3을 양쪽 모두 지원한다. PCI Express 레인 수는 32. Monolake 플랫폼 전용 SKU가 될 것으로 보인다.

또한 Intel Ark에는 TDP 45W로 16코어 "Xeon D-1571"과 "Xeon D-1577", 12코어 "Xeon D-1557"과 "Xeon D-1567"(TDP 65W)의 제품 정보도 조용히 추가되었다.

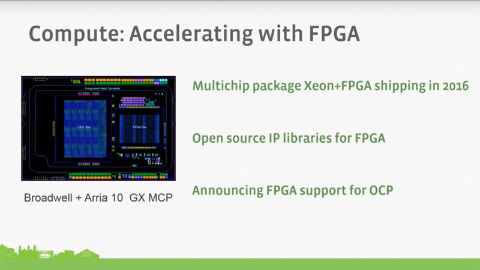

그리고 두번째는 인텔이 인수한 알테라의 FPGA "Arria 10 GX"를 MCP로 1개의 패키지로 통합한 제온이다. 강연에서 제시된 슬라이드를 보면 15코어 Broadwell-EP를 통합하며 이 Xeon은 이미 샘플 출하가 시작되고 있다. 다만 영상만으로는 대응 소켓은 불명이다. 적어도 LGA2011-v3는 아닌 것 같다.

현재 데이터 센터는 FPGA 채용이 초점의 한가지다. 인텔은 제온과 Arria 10 GX를 통합함으로써 데이터 센터에 Altera FPGA를 침투시키려는 의도가 있을 것이다.

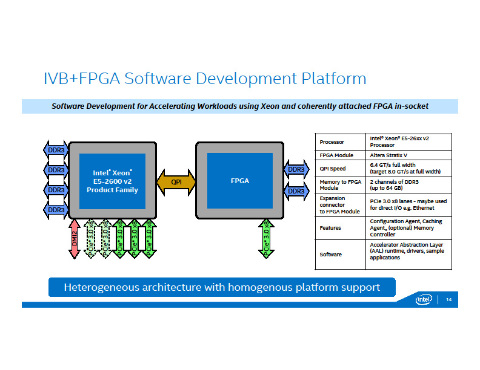

아래 슬라이드는 ISCA 2015(42회 International Symposium on Computer Architecture)에서 제시된 Ivy Bridge와 FPGA을 통합시키는 구상을 나타낸 슬라이드로 FPGA와 CPU는 QPI로 연결되는 것으로 나타났다.

참고로 알테라는 "EMIB(Embedded Multi-die Interconnect Bridge)" 라는 인텔의 새 패키지 기술을 채택하여 다른 다이(반도체)을 1패키지로 제안했다. 이 제온도 EMIB을 채용한 가능성이 있을 것으로 볼 수 있지만 슬라이드는 "MCP"라고 쓰여 있으므로 다른 것으로 보인다.

출처 - http://pc.watch.impress.co.jp/docs/news/20160408_752237.html

'글로벌 IT 뉴스' 카테고리의 다른 글

| 인텔이 제안하는 원할한 데이터 서비스 인프라 (3D XPoint) (0) | 2016.04.20 |

|---|---|

| 엔비디아 드라이브PX2, 로봇 자동차 경주에 제공 (0) | 2016.04.11 |

| 엔비디아 파스칼 아키텍처, 혁신적인 GPU의 이정표 (0) | 2016.04.08 |

| 인텔 틱톡 전략 변경, 새로운 3번째 단계 Optimization 추가 (0) | 2016.04.01 |

| 윈도우에 우분투 Bash 지원, 마이크로소프트 Build 2016 (0) | 2016.04.01 |