AMD 3세대 Ryzen, Radeon 'Navi' 컴퓨텍스 발표?

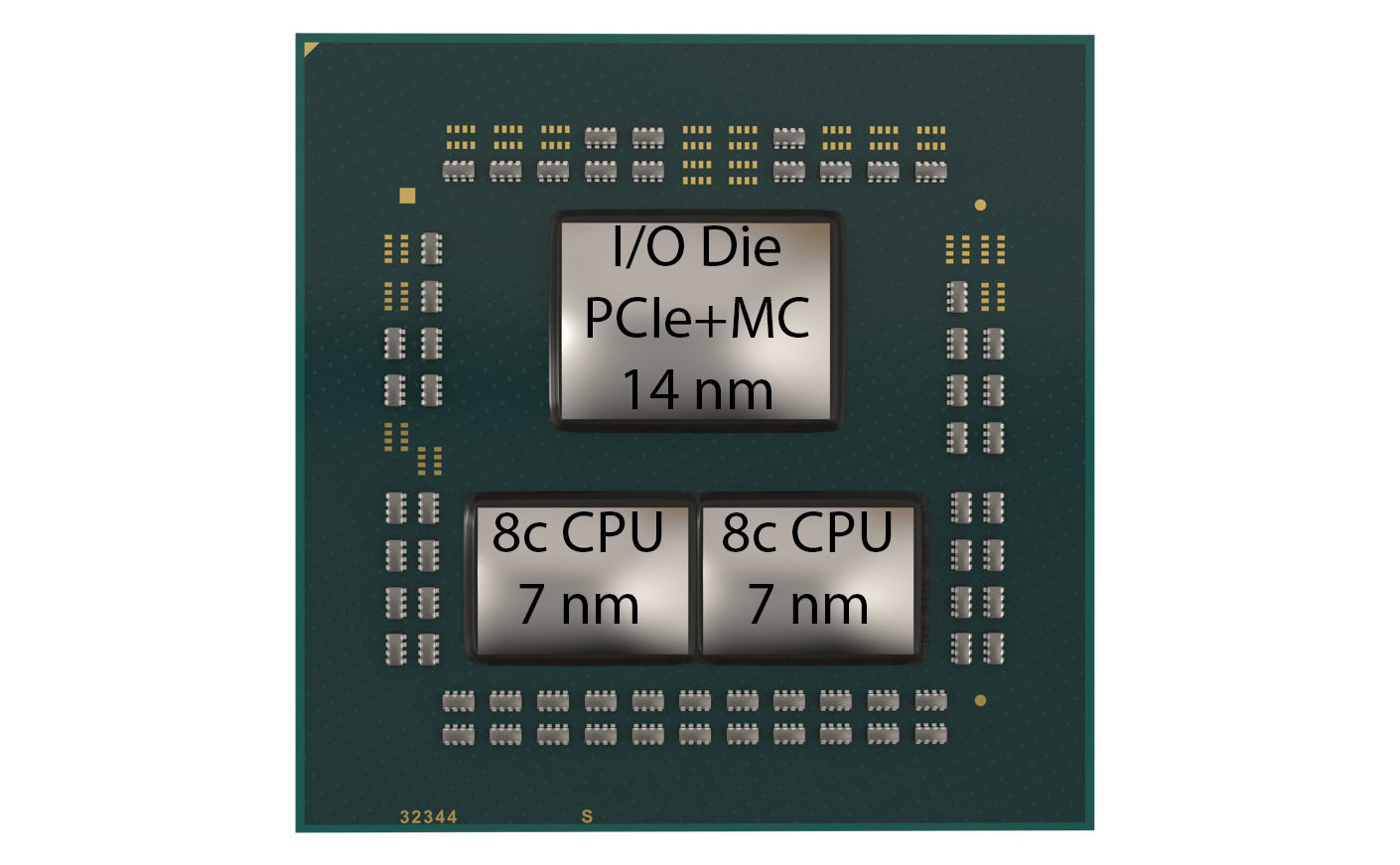

매년 6월 대만 타이페이에서 개최되는 컴퓨텍스(Computex) 트레이드 쇼의 운영기구 TAITRA는 AMD CEO 리사 수(Dr. Lisa Su)가 CES 기조 연설만큼 흥미로운 기조 연설을 할 것이라고 발표했다. 리사 수는 적어도 네 개의 제품 라인을 동시에 출시하거나 발표 할 예정이다. AMD는 "Zen 2" 마이크로 아키텍처와 "마티스" 라는 코드 명을 가진 멀티 칩 모듈 (MCM)을 기반으로 한 소켓 AM4 패키지의 3세대 Ryzen 데스크탑 프로세서에 대한 의제를 공개했다. 이 런칭은 "로마" MCM 기반의 2세대 EPYC 엔터프라이즈 프로세서와 관련된 주요 발표로 이어질 수 있다.

또한 이번에 RTG는 두 번째로 중요한 발표를 할 예정이다. Radeon "Navi"는 7nm 실리콘 제조 공정을 기반으로 설계된 GPU. 마지막으로 Radeon Instinct DNN 가속기의 변종도 발표 할 수 있다.

'글로벌 IT 뉴스' 카테고리의 다른 글

| Google 하이브리드 클라우드 안토스(Anthos)로 AWS, Azure 통합 가능 (0) | 2019.04.27 |

|---|---|

| 인텔, 모바일 8세대 인텔 코어 v프로 프로세서 발표 (0) | 2019.04.27 |

| 블록체인 기술 응용, 암호화 및 용장성을 겸비한 NAS 출자 (0) | 2019.04.27 |

| 게임 월 정액제 서비스 애플 아케이드(Apple Arcade) 발표 (0) | 2019.04.14 |

| Apple Pay 크레딧 카드 기능 애플 카드(Apple Card) 발표 (0) | 2019.04.14 |