AMD 젠 아키텍처 공개, 인텔을 넘어설까? (서밋릿지)

Zen의 세부 사항은 다음주 회의에서 발표

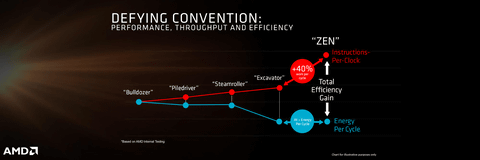

AMD는 고성능 CPU 시장 점유율을 탈환하기 위한 수단으로 차세대 x86 CPU "젠(Zen)"을 투입한다. Zen은 현재의 불도저계 CPU 코어 "Excavator(엑스카베이터)" 보다 40%의 클럭당 정수 명령 실행 성능이 높아진다. 또 AMD의 CPU에서는 처음으로 SMT(Simultaneous Multithreading)를 지원하여 2쓰레드를 1코어로 실행 가능하다. 14nm FinFET 프로세스에서 제조되기 때문에 AMD의 28nm 현행 APU와 40nm의 현행 CPU보다 성능/전력이 비약적으로 향상된다.

AMD는 미국 샌프란시스코에서 프레스 컨퍼런스를 개최, Lisa Su(리사수, President and Chief Executive Officer, AMD)와 기술 부분을 이끄는 Mark Papermaster(마크 페이퍼마스터, Senior Vice President and Chief Technology Officer, AMD)이 등장하여 젠을 발표했다. 이 회사는 다음주 칩 컨퍼런스 "Hot Chips"에서 젠의 상세 내용을 발표할 예정이지만 그 개요를 조기 공개했다.

정공법, 마이크로 아키텍처로 공격하는 Zen 프로세서

AMD는 젠 아키텍처를 높은 성능, 산출량, 효율을 염두하고 설계했다고 설명했다. 기존 Bulldozer형 아키텍처는 싱글 스레드 성능을 어느 정도 막고 전력과 다이 면적당 성능을 추구했다. 반면 Zen은 싱글 스레드 성능을 추구하면서 성능 효율을 높인 점이 다르다.

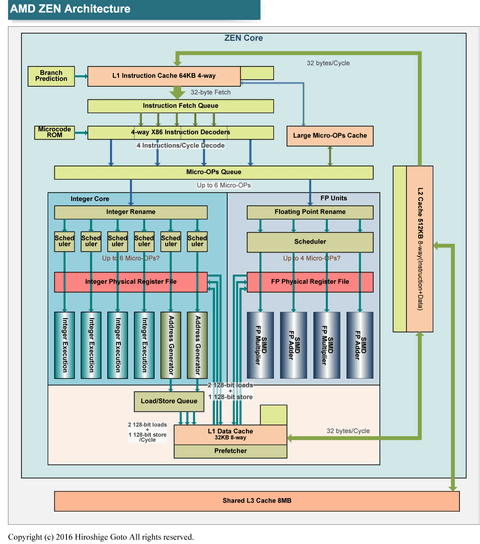

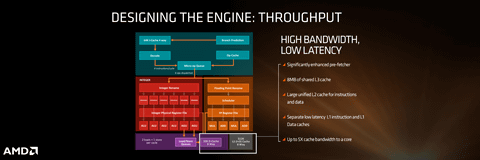

CPU 아키텍처를 보면 그 설계 사상을 알 수 있다. Zen은 스트레이트 포워드 즉, 정공법으로 아키텍처를 조립하고 있다. 4명령/사이클의 명령 해독기에서 x86/x64 명령을 내부 명령 Micro-Op/uOP에 디코드, uOP를 정수와 부동 소수점 연산계로 크게 2개로 나누어진 스케줄러에서 처리한다. 처리 대역은 최대 6 uOPS/사이클이다.

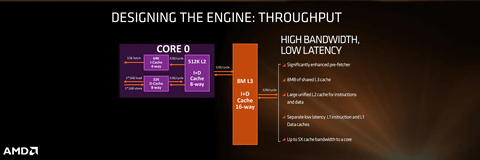

정수 계열은 4연산 파이프와 2주소 생성 파이프, FP계는 SIMD(Single Instruction, Multiple Data)의 FP곱하기와 FP가산의 쌍이 2개 4파이프. 메모리 계층은 64KB의 L1 명령 캐시와 32KB의 L1 데이터 캐시, 512KB의 L2 캐시와 코어 사이에서 공유하는 8MB의 L3 캐시에 추가 명령 디코더의 하류에 uOP 캐시를 갖춘다. 아키텍처적으로는 Intel CPU와 설계가 비슷한 부분도 많다.

Bulldozer계의 CPU코어는 쓰레드당 정수 연산 파이프가 2개였다. 그것에 비해 젠은 정수 연산 파이프는 4개로 배가량 늘었다. AMD의 현재 CPU코어 "Excavator" 보다 클럭당 정수 계열의 명령 실행 성능 IPC(Instruction-per-Clock)는 40%나 높아진다. 참고로 K10 까지의 옛 AMD 아키텍처는 정수 연산 파이프가 3개다. 4개의 정수 연산 파이프는 AMD 아키텍처에서는 처음이다.

Micro-Op/uOP 캐시를 갖춘 Zen 프론트 엔드

Zen의 프론트 엔드는 L1명령 캐시는 64KB의 4-way에 L1으로부터 명령 페치는 32바이트 폭이다. 명령 해독기는 4-way로 최대 4개의 x86/x64 명령을 디코딩 할 수 있다. 종래대로 명령 퓨전을 장착하고 있다면 분기 명령 등을 융합시키는 것으로 최대 5명령 부분을 디코딩 하는 것이 된다. x86/x64 명령을 디코딩 하여 생성된 내부 명령 Micro-Op/uOP는 큐에서 큐잉되고 프론트 엔드에서는 분기 예측도 강화됐다.

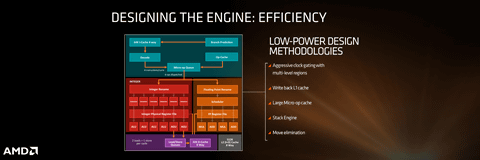

Zen의 프론트 엔드에서 기존 AMD 아키텍처에 없던 것은 "uOPs Cache"로 디코딩 한 uOPs를 캐시한다. 가변 길이로 다양한 명령 형식이기 때문에 명령 디코딩이 복잡하게 되는 x86/x64명령의 디코딩을 생략하고, 디코딩을 마친 uOPs를 캐시 함으로써 효율적인 명령 피드를 실현한다. 전력 소비가 많은 명령 디코딩을 건너 뛰기 때문에 전력 절약 측면에서의 효과도 크다. AMD는 큰 uOP 캐시라고 설명하고 있기 때문에 수십 명령 정도의 루프 캐시가 아니라는 것을 알 수 있다.

인텔도 같은 구조를 가지고 있으며 uOPs 캐시의 태그가 L1 명령 캐시의 태그와 연결되고 있다. L1 명령 캐시를 매핑하는 히트 로직을 채용하는 것으로, 트레이스 빌드 등을 하지 않는 심플한(단, 소모도 많다)제어를 하고 있다. 현재의 스카이레이크의 경우 uOP 캐시 메모리에는 64바이트 분량의 L1 명령 캐시 페치 윈도우를 매핑하고 있다.

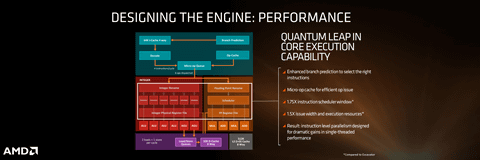

Micro-Op/uOP 큐에서는 1사이클에 6개의 uOPs를 스케줄러에서 처리할 수 있다. 만약 명령 해독기가 4 uOPs/사이클 밖에 디코딩을 못하면 복호화 대역으로 벗어나게 된다. 더구나 uOP캐시에서 페치가 최대 6 uOPs의 가능성도 있다. 인텔의 스카이레이크도 Micro-Op/uOP 캐시로 히트한 경우 최대 6 uOPs를 페치 할 수 있다. 기존의 Bulldozer계 CPU 코어는 스케줄에 대해 4 uOPs 처리기 때문에 AMD는 Zen이 1.5배의 명령 대역이라고 설명했다.

그리고 x86/x64 CISC(Complex Instruction Set Computer)명령을 실행하는 AMD CPU는 기존에는 마이크로 오퍼레이션을 복합시킨 Macro-OP를 스케줄 단계에서 운영 단위의 Micro-OP로 변환하는 스타일을 취했다. 내부적으로도 CISC 형태였다. Zen의 경우는 아직 어떤 uOPs로 구성되어 있는지는 모른다.

4개의 정수 연산 파이프의 Zen 정수 코어

Zen의 정수 코어 구성은 4개의 정수 연산 파이프에 2개의 로드/스토어 파이프의 구성, 기존 Bulldozer계 코어는 2개의 정수 연산 파이프와 2개의 로드/스토어 파이프다. 그래서 AMD는 Zen에는 실행 자원이 1.5배가 되었다고 주장하고 있다. 파이프를 늘렸을 뿐만 아니라 AMD는 명령의 스케줄링 윈도우도 1.75배로 했다. 다만 이는 1코어당 비교일 가능성이 있다. AMD는 Zen에서 보다 큰 1코어에서 2쓰레드를 실행하는 구조여서 쉽게 비교할 수 없다. 더 자세히 보면 Zen 코어는 스택 오퍼레이션을 위한 하드웨어 엔진을 갖는 Move 명령의 엘리미네이션도 한다.

FP 연산 파이프에 대해서는 아직 모른다. AMD는 Zen에서 부동 소수점 연산 성능도 크게 향상된다고 설명했다. AMD 슬라이드 상에서의 구성은 곱셈 유닛이 2개에 가산 유닛이 2개. 곱셈 유닛과 가산 유닛을 조합함으로써 주산 명령을 실행할 것으로 보인다. SIMD(Single Instruction, Multiple Data)유닛이지만 SIMD폭은 아직 모르지만 256-bit 4유닛으로 예상된다.

로드/스토어는 주소 생성 유닛이 2유닛. 다만 2로드와 1스토어를 병렬 실행할 수 있다고 생각되고 있다. L1 데이터 캐시는 32KB로 8-way. 데이터 캐시 메모리에는 프리페처가 있는데 Zen 에서는 이것이 대폭 강화됐다. 더 복잡한 데이터 패턴을 선반입할 것으로 예상된다.

스레드 병렬을 SMT(Simultaneous Multithreading)로 전환한 Zen

캐시 계층은 L0에 해당하는 uOP 캐시라 웬만한 용량의 L1, 상대적으로 작은 L2, 대용량으로 코어 간에서 공유 L3의 4단계 구성이다. L2를 줄이면서 L2 접속 레이턴시는 크게 단축됐다고 보인다. 캐시 계층은 Intel CPU 캐시 계층과 거의 비슷하다. 캐시 대역은 L1 명령 캐시에서 페치가 32-byte(256-bit)/사이클. L1 데이터 캐시에서 2개 16-byte(128-bit) 로드와 1개 16-byte(128-bit) 스토어를 병렬 실행 가능하다. L2의 대역은 L1 명령 캐시와 L1 데이터 캐시가 각각 32-byte(256-bit)/사이클.L3와 L2 사이도 32-byte(256-bit)/사이클이다.

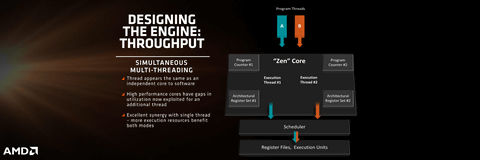

스레드 병렬성에서 Zen은 SMT(Simultaneous Multithreading)를 구현하여 2쓰레드를 혼재 실행할 수 있다. Bulldozer형 아키텍처에서 스레드마다 독립된 정수 코어를 갖춤으로써 2쓰레드를 병렬 실행했다. Bulldozer계에서는 FP 유닛과 L2 캐시를 2스레드에서 공유하고, 메인 정수 유닛은 스레드마다 독립시킨 구성이었다. 반면 Zen에서는 큰 싱글 코어에서 2쓰레드를 병렬 실행한다. 인텔의 Hyper-Threading과 기본적인 부분은 같다.

2개의 스레드는 각각 독립된 프로그램 카운터를 갖고 아키텍처 레지스터 파일도 개별된다. 실제로 아키텍처 레지스터는 물리 레지스터 파일에 리네이밍 장치에서 매핑한다. 각각의 스레드 명령은 아웃 오브 오더 실행 엔진에서 병렬 실행된다.

데스크탑용은 8코어 Summit Ridge

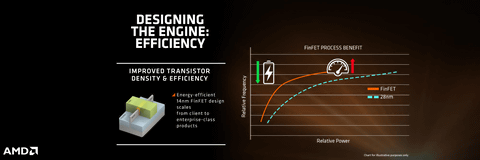

Zen의 제조 공정 기술은 14nm 노드. 글로벌 파운드리의 14LPP 로 보인다. AMD의 CPU나 APU(Accelerated Processing Unit)에서는 첫 FinFET 3D 트랜지스터 프로세스가 된다. AMD는 APU가 28nm, CPU가 40nm 프로세스였으므로 14nm의 FinFET 프로세스로의 이행은 큰 점프다. 누설 전류(Leakage)가 떨어질 뿐 아니라 일정한 동작 주파수때 액티브 전류도 떨어지기 때문에 큰 폭으로 전력 절약이 된다.

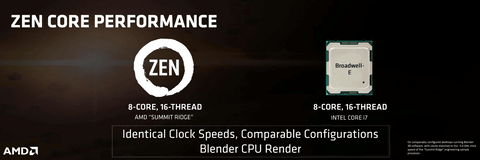

AMD는 동작 주파수당 전력 소비는 현재의 CPU 코어 Excavator과 동등하며 IPC(Instruction-per-Clock)가 40% 나 오른다고 강조한다. 또 AMD는 앞으로 Zen 코어를 발전시키며 더 실행 효율을 높인 "Zen+"가 예정되어 있다.

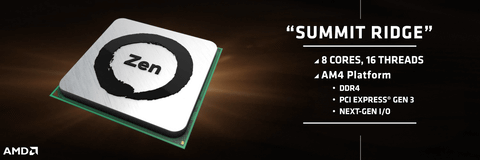

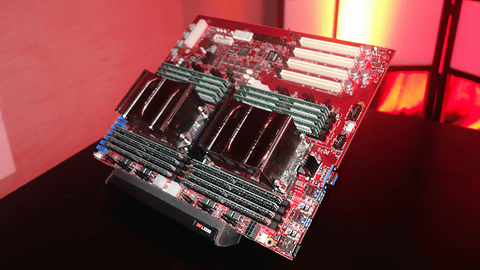

먼저 제품화되는 것은 하이엔드 데스크탑용 "Summit Ridge(서밋 릿지)". 8코어에 16스레드의 CPU 제품이다. 소켓 플랫폼은 "AM4", 메모리는 DDR4, I/O는 PCI Express gen3, 아직은 공개되지 않은 칩간 인터커넥트를 갖춘다. 게이밍과 VR(Virtual Reality), 워크 스테이션 등의 시장을 노린다.

또 AMD는 32코어 서버 SoC(System on a Chip) "Naples"도 공개했다. SMT로 64스레드의 몬스터 CPU다. 구성을 감안하면 4개의 Summit Ridge 다이를 연결할 가능성도 있다. AMD가 공개한 것은 Naples의 2소켓 서버였다.

또 AMD는 앞으로 Zen 베이스의 APU(Accelerated Processing Unit)도 투입한다. 메인 스트림의 데스크톱과 노트북 PC 또 임베디드까지 Zen을 가져온다. AMD에게 지금까지는 획기적인 CPU나 APU가 없는 어려운 시기였지만 Zen의 투입으로 상황을 바꾸려 하고 있다.

출처 - http://pc.watch.impress.co.jp/docs/column/kaigai/1015633.html

'글로벌 IT 뉴스' 카테고리의 다른 글

| 마이크로소프트 파워쉘을 오픈 소스화 (PowerShell) (0) | 2016.08.20 |

|---|---|

| 제온파이가 GPU보다 빠르다는 주장에 엔비디아가 발끈 (0) | 2016.08.19 |

| 인텔의 인공지능, 제온과 제온파이 나이츠 밀 (IDF) (0) | 2016.08.18 |

| 네트워크도 인텔 인사이드, 실리콘 포토닉스 투입 (랙스케일 아키텍처) (0) | 2016.08.18 |

| 인텔과 ARM이 파운드리 제휴 발표, 10나노 커스텀 (0) | 2016.08.18 |