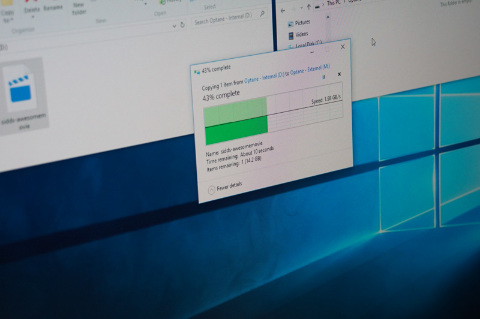

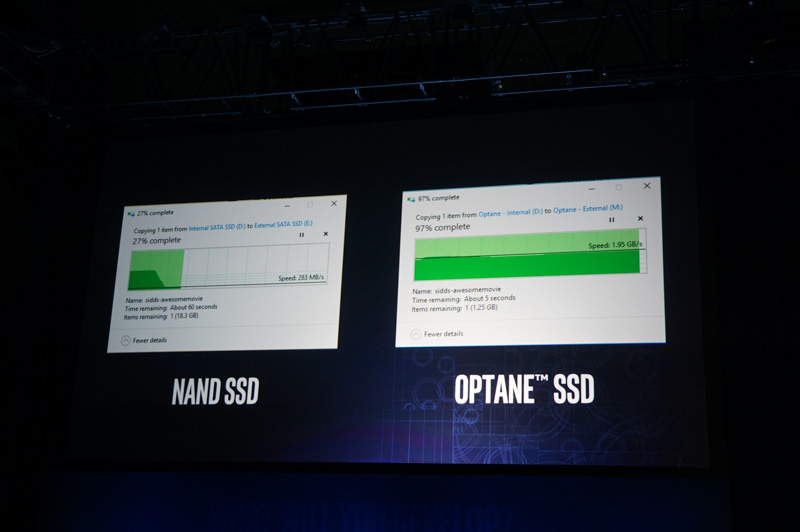

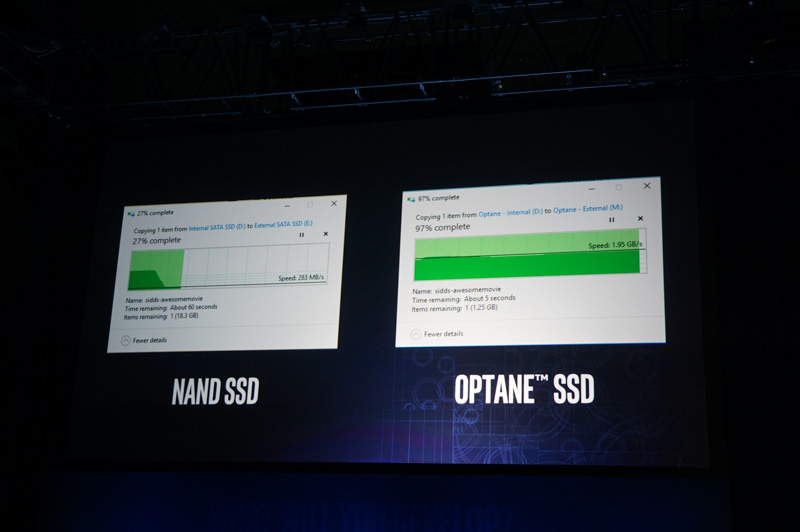

실제 환경에서 2GB/sec를 넘는 전송 속도를 보인 OPTANE SSD

인텔은 개발자를 위해 개최하는 기술 이벤트 "Intel Developer Forum(IDF)"를 중국 선전 시내의 호텔에서 진행했다. 봄에 열리는 IDF 선전은 주로 중국에 집중되어 있는 ODM 업체 등을 겨냥하고 있어 올해(2016년)에는 로봇이나 헬스 케어로 불리는 새로운 사용자 모델을 위한 내용이 중심이 됐다.

첫날에는 인텔의 현지 법인인 인텔 차이나 사장 및 인텔 본사 부사장인 이안 양과 인텔 부사장겸 데이터 센터 사업 본부장 다이언 브라이언트에 의한 강연이 열렸다. 이중 이안 양은 3D XPoint을 시연하고 그 전송 속도가 2GB/sec를 넘는걸 과시했다.

큐리와 리얼센스를 바탕으로 한 로봇이나 드론 전용 개발 킷 발표

이언 양은 IDF 16 선전의 기조 강연에서 디지털화, 클라우드 컴퓨팅, 스마트 인터넷에 접속된 세계의 확대라는 3가지 주제에 따라 이야기를 진행했다.

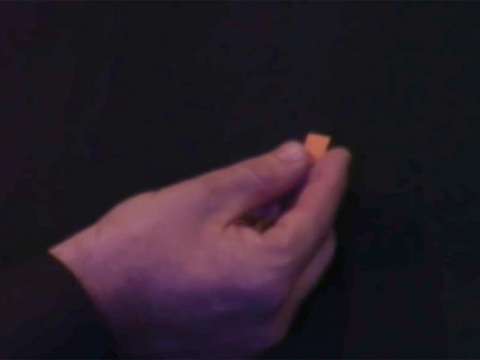

디지털화라는 관점은 큐리와 리얼센스에 대한 화제를 소개했다. 큐리는 단추 크기의 초소형 칩으로 지난해(2015년) CES에서 발표된 제품. 구체적인 개발 예로 여자가 붙이고 있는 Curie 디바이스에서 손과 발의 움직임을 데이터화하고 실시간으로 표시하는 패턴 매칭 시연 등이 진행됐다.

이언 양은 "큐리에 복수의 개발킷과 SDK 등을 제공한다"며 USB와 BLE(Bluetooth Low Energy)를 연결하고 개발에 사용할 수 있는 Genuino 101 보드를 포함 "Curie Board Support Package(BSP)", OEM/ODM 업체들의 개발을 용이하게 하는 "Intel iQ 소프트웨어 킷" 머신러닝이나 패턴 매칭 등을 쉽게 만들수 있는 "Intel Knowledge Builder Toolkit" 등의 제공을 발표했다.

또 인텔이 추진 중인 3D 카메라 솔루션 "RealSense"에 대해 1월 CES 기조 강연에서 공개된 RealSense를 로봇의 눈으로 이용하고 있는 세그웨이 로봇을 소개하는 등 RealSense가 PC 외에도 사용할 수 있는 점을 과시했다. "지금까지도 Intel RealSense 개발 킷을 제공했는데 그것은 Windows용이었다. 이제는 오픈 API로 Linux, Android, OS X, Windows를 지원한다"고 밝혔다.

또 로봇 개발을 RealSense에서 하고 싶은 개발자에게 "Intel RealSense ROBOTIC Development Kit"을, 드론 개발자에게 "Intel Aero Platform for UAV"를 제공한다. 저렴하게 로봇이나 드론 개발을 할 수 있게 된다고 어필했다.

두번째 주제는 클라우드 컴퓨팅의 확대. 이안 양은 "현재 클라우드 컴퓨팅으로 말하면 스마트 폰이나 PC에서 이용한다는 이미지라고 생각하지만 가까운 장래에 IoT 기기도 클라우드를 이용하게 되고, Cloud of Things의 시대가 올것" 이라며 클라우드 컴퓨팅과 IoT를 조합함으로써 보다 편의성이 높은 세계가 온다고 설명했다.

그 예로 NBA 농구 경기를 복수의 카메라로 촬영하여 시청자가 시점을 자유롭게 전환하는 시연을 선 보였다. 심지어 인텔이 제공하고 있는 IoT 개발 환경 Intel IoT Platform을 기반으로 한 중국 정부나 중국의 병원이 협력하여 개발한 사례 등을 소개했다.

3D XPoint기반의 인옵테 SSD를 윈도우PC에서 시연, 약 2GB/sec라는 전송 속도를 실현

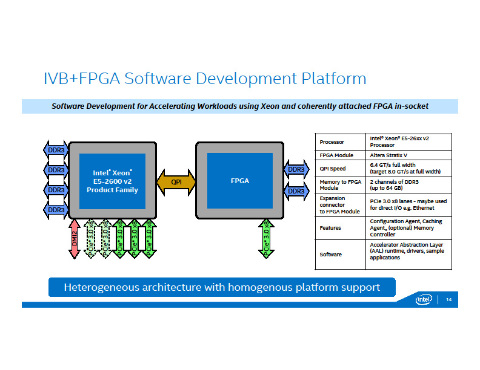

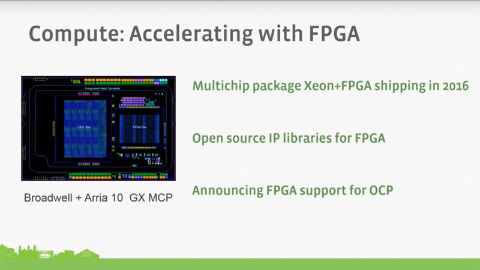

세번째 스마트 인터넷에 접속된 세계의 확대란 부분은 주로 인텔이 지난해 인수를 발표한 FPGA 업체인 Altera(알테라)와 협업에 대한 설명이 진행됐다. 이안 양은 현재 컴퓨터 업계에서 큰 화제가 되고 있는 기계 학습(기계에 의한 자동 학습)을 언급하며 그 솔루션으로서 Altera의 FPGA을 탑재해 엑셀러레이터로 이용할 수 있다고 어필했다. 또한 인텔은 "Arria 10 FPGA"와 "Xeon E5 v4"를 1패키지로 만든 제품을 이미 발표하고 있으며 14nm 프로세스에서 생산된 Stratix 10을 넣은 제품은 4분기에 출하한다.

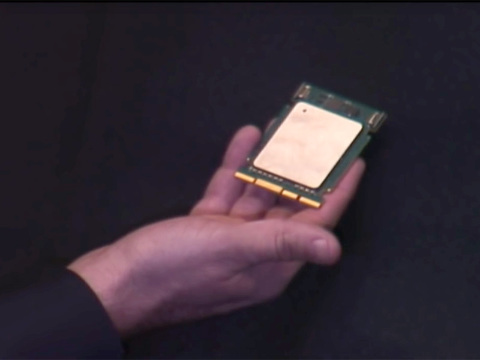

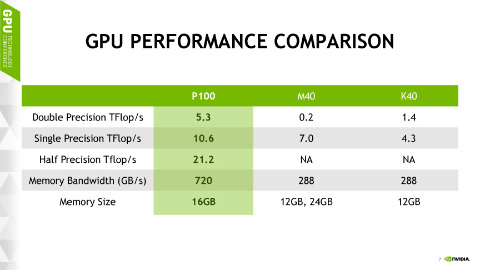

그 뒤 NAND 플래시 메모리를 언급하며 인텔이 처음으로 3D NAND 플래시 메모리로 제조한 엔터프라이즈용 SSD를 발표하고 향후 현재의 NAND 플래시 메모리보다 더 큰 고속화가 실현되는 3D XPoint Technology 기반 제품의 투입도 밝혔다. 인텔의 부사장 겸 NV메모리 솔루션 사업부장 롭 클락을 단상에 불러 3D XPoint의 장점 설명과 시연이 진행됐다.

이 가운데 롭 클락은 옵테인 브랜드 이름으로 판매될 예정의 3D XPoint를 이용한 SSD 샘플을 탑재한 PC를 공개하고 Thunderbolt 3로 접속되고 있는 외장 옵테인 SSD에 데이터를 복사하는 시연을 보였다. 그 카피 속도는 약 2GB/sec(화면상에서는 1.9xGB/sec으로 표시)로 기존의 NAND SSD에 비해 압도적으로 고속이었다. 물론 이것은 초기 샘플의 시연이며 실제 제품은 더 빨라질 것으로 예상된다.

이안 양은 인텔이 중국 다롄에 있는 공장에 대한 투자를 이어 간다며 향후 3~5년 동안 35억달러를 투자한다고 중국 관계자들에게 어필했다.

출처 - http://pc.watch.impress.co.jp/docs/news/event/20160413_753106.html