핀펫(FinFET) 트라이게이트 반도체 공정의 탄생

|

|---|

| 트랜지스터의 구조 |

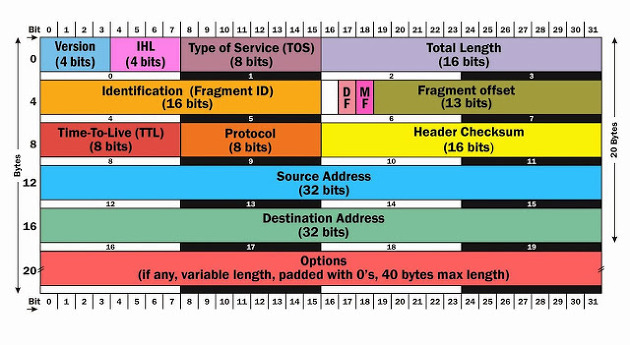

면적은 게이트장에 비례하는 것으로 게이트를 짧게 하면 콘덴서의 용량이 줄어들고 결과적으로 구동 전류가 줄어드는 현상이 생긴다. 더 높은 K(비유 전율)을 가진 High-K 재료가 갑자기 발견되면 문제가 없겠지만 현재 40 가까운 값의 K도 10년 이상 연구를 거듭하여 가까스로 발견한 것이기 때문에 이를 넘는 재료의 발견은 그리 쉽지 않다.

이런 문제를 해결할 수 있도록 고안된 것이 3차원 트랜지스터다. 인텔은 "트라이게이트 트랜지스터"라고 부르는데 일반적으로는 핀펫(FinFET)이라 불리는 경우가 많다.

|

아이비 브릿지 발매 기념 이벤트에서 전시된 트라이 게이트 트랜지스터를 소개한 모형 |

|---|

원래 핀펫이라는 구조를 고안한 것은 히타치며 1989년에 IEDM이라는 학회에서 처음으로 이 구조를 제안했다.

참고로 당시는 핀펫이 아닌 DELTA라는 명칭이었다. DELTA란 "a fully DEpleted Lean channel TrAnsistor"에서 따왔다. 위의 논문 제목은 "Impact of the vertical SOI`DELTA'structure on planar device technology"며 원래는 SOI용 구조로서 생각된 것이다.

실제로 핀펫은 원리적으로 SOI와 궁합이 좋지만 SOI와 관련된 이야기는 다음에 설명하기로 한다.

이 DELTA의 영향으로 다양한 반도체 메이커나 파운드리가 3차원 구조의 트랜지스터로 눈을 돌리게 됐다. 1990년대 후반~2000년에 걸쳐 많은 업체가 3차원 구조 트랜지스터에 관심을 갖기 시작했다.

|

평면형 트랜지스터(왼쪽)과 트라이게이트 트랜지스터의 전류가 흐르는 경로 이미지. 노란 색이 전류를 나타낸다 |

|---|

인텔도 2002년의 IDF 기조 강연에서 트라이게이트 트랜지스터를 발표했다. 이 시기는 CPU 동작 주파수를 10 ~ 20GHz를 전망하던 시기며 이를 실현하기 위해서는 트랜지스터의 동작 주파수 자체는 더 고속으로 움직이지 않으면 안됐다.

1개의 4출력 게이트는 NOP가 2개분(실제로는 5개지만 4개는 병렬로 나란히 있는 것으로 직렬 방향으로는 2개가 된다)이며 NOP는 1개의 트랜지스터로 구성된다(이것도 최저 2개지만 병렬이므로 레이턴시라는 관점에서는 1개 상당)이라고 합하면 20개의 트랜지스터가 직렬로 연결된 형태다.

만약 동작 클럭이 10GHz로 움직이려고 하면 트랜지스터 1개당 200GHz로 동작하지 않으면 않된다. FO4가 10이라는 것은 파이프 라인이 상당히 깊어진 구성으로, 반대로 FO4가 30정도에서도 10GHz 동작이 가능하도록 설계한 경우 트랜지스터는 600GHz에서 동작할 수 있는 것이 필요하다.

이러한 점을 감안하고 인텔은 1THz에서 동작하는 "테라헤르츠 트랜지스터"에 관한 기술 개발을 2001년 11월에 발표하고 있다.

|

테라헤르츠 트랜지스터의 구조와 장점 |

|---|

이 기사에도 있듯이 당시는 2007년에 20GHz 라는 무서운 구동 속도를 실현하는 것을 전망하여 1THz의 구동 성능은 필수였다.

설명을 다시 트라이게이트로 되돌리면 테라헤르츠 트랜지스터를 기존의 평면 구조로 구성하면 아무래도 어려운 요소가 있었는데 그것은 실리콘 층의 두께를 제어하는 문제다. 그 문제를 해결하는 것이 2002년 발표된 트라이게이트 트랜지스터 구조다.

|

실리콘 층의 두께를 제어하는 문제는 그 후 90nm 과정에서 표면화 된다. 이 때는 멋지게 두께 자체는 제어할 수 있었지만 그것에 따른 문제를 해결할 수는 없었다 |

|---|

|

| |

|---|---|---|

| 게이트와 소스/드레인이 교차하는 부분의 그림 |

먼저 이 당시는 인텔 이외에도 많은 벤더가 3D 구조에 도전했다는 이야기는 말한 그대로지만, 실은 AMD는 이 발표의 2일 전에 더블 게이트 트랜지스터라고 하는 구조를 발표했다.

AMD는 인텔보다 위에 노출되는 부분을 줄이고 좌우만을 형성하는 구조다. 인텔은 더블 게이트보다 자사의 트라이 게이트 구조가 효율이 더 좋다고 설명했다.

|

트라이 게이트의 이점. 높이와 두께에 비례하여 트라이 게이트에서는 채널장이 많지만 더블 게이트는 두께 부분에 게이트가 없는 만큼 길이가 줄어든다는 것을 나타낸다. |

|---|

구체적으로는 트라이 게이트의 경우는 두께를 비교적 크게 해도 동작하지만 더블 게이트는 얇게 하지 않으면 안 되는 것이 단점이라고 지적했다.

|

| |

|---|---|---|

| 트라이 게이트의 구조. 그림은 비유며 높이와 두께가 동일할 필요는 없다. 요컨대 두께를 비교적 크게 잡는 것이 이득이라는 것 | 더블 게이트의 경우 두께를 얇게 하지 않으면 효과가 나쁘고, 얇게 만드는 것이 제조적으로 어려운 것이 흠 |

이야기를 다시 3D구조로 돌아오면 3D 구조 방식의 메리트는 복수의 FET 병렬 구조를 간단하게 만들기 쉽다 라는 점이 꼽힌다. 게이트가 공통이므로 다른 회로를 구성할 수는 없지만 반대로 많은 출력이 필요한 경우에는 특성이 가지런한 멀티 채널 드라이버 구성이 가능하다는 것이다.

|

3D 구조 방식의 장점. 높은 출력이 필요한 경우 일반적으로 트랜지스터를 병렬로 다수 늘어놓지만 3D 구조에서는 이것을 정리해 만들기가 쉽다 |

|---|

여기까지는 2002년 시점의 내용으로 트랜지스터도 어디까지나 실험실 레벨에서 제조에 성공했다는 이야기였다. 이를 실제 22나노 프로세스를 적용해 공개한 것은 2011년 5월 인텔이다.

이 때 인텔은 꽤 대대적으로 설명회를 진행했다. 개인적으로는 아래 영상의 3분 10초 이후를 보면 기존 평면형과 트라이 게이트의 차이를 가장 알기 쉽게 이해할 수 있다고 생각한다.

그런데 22나노 구현의 기본적인 부분은 지금까지와 다르지 않다. 베이스가 되는 것은 32나노 세대의 P1268이다. 이것은 HKMG와 파행 실리콘의 구성으로 게이트장은 18나노였다. P1268을 그대로 미세화하면 22나노 세대에서는 게이트장이 12나노 정도다.

|

| |

|---|---|---|

| 22나노 세대는 게이트장이 12나노 정도. 본 기사의 처음에 게재한 트랜지스터의 구조 그림은 이 구조를 옆에서 본 형태 |

그런데 여기서 소스 ⇔ 드레인 사이를 3차원화 하면 게이트장 자체는 12나노에서 변하지 않으며 High-K막에서 보호된 절연 부분의 면적을 크게 하여 실질적인 면적을 늘릴 수 있다.

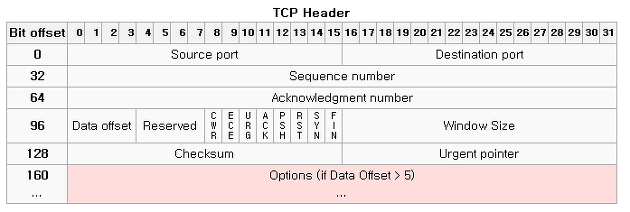

이 구조에서 동작 종료시 공핍층이라 불리는 영역이 거의 완전히 차단되는 것도 핀펫의 특징이다. 핀펫에서는 공핍층을 막는 것으로 보다 고속 동작이 가능하다. 실제로 수치로 나타낸 것이 아래 그래프.

|

게이트 전압과 흐르는 전류의 관계를 정리한 것 |

|---|

구체적으로 32나노(P1268)와 22나노 및 P1270(22나노의 테스트 게이트)를 비교했을 경우, 같은 동작 전압이면 게이트 지연을 18~37% 절감할 수 있고, 반대로 같은 정도의 지연이면 동작 전압을 0.2V 절감할 수 있다.

|

| |

|---|---|---|

| 1V를 0.8V로 줄이면 소비 전력은 전압의 2제곱에 비례하기 때문에 그것만으로 0.6배 정도 된다. 이것이 더 개발되면서 동작시 소비 전력이 50% 절감된다 |

이 트라이 게이트 트랜지스터는 22나노부터 인텔만 사용하고 있는 기본적인 구성이다. 인텔은 22나노 세대에서 크게 4종류의 프로세스를 제공하고 있으며 트랜지스터만 봐도 HP(High Performance)/SP(Standard Performance/Power)/UP(Low Power)의 3종류가 제공된다.

|

| |

|---|---|---|

| 인텔은 22나노 세대에서 크게 4종류의 프로세스를 제공했다. 주된 차이는 배선층 밀도지만 물론 밖으로도 많은 차이는 있다 |

인텔은 세부적인 부분을 말하지 않지만 현재 핀펫의 구조 자체를 크게 바꾸지 않고 14나노 세대에도 계속 제공해 나간다.

|

| |

|---|---|---|

| 기존에는 채널장을 세세하게 조정하고 특성을 바꿀 수 있었지만(왼쪽), 핀펫 세대에서는 불가능하다 | 인텔 이외의 파운드리들은 채널장을 바꿀 수 없기에 특성을 조정한다 |

보도 - http://ascii.jp

'글로벌 IT 뉴스' 카테고리의 다른 글

| 2015년 세계 반도체 파운드리 점유율 (TSMC) (0) | 2016.04.25 |

|---|---|

| 웨어러블 컴퓨터 / 유비쿼터스 컴퓨팅 / 인텔 에디슨 및 쿼크 (0) | 2016.04.25 |

| 로지텍 G900, 유무선 대응 전략 마우스 (0) | 2016.04.23 |

| GPU 도킹 스테이션 레이저 코어 발표 (0) | 2016.04.23 |

| 시놀로지 소형 나스, 디스크 스테이션 DS416 slim 발매 (0) | 2016.04.23 |