인텔, 차세대 CPU 아키텍처 서니코브, 윌로우 코브, 골든 코브 발표

미국 Intel은 11일(현지시간) 로버트 노이스의 과거 사저에서 기자회견을 열고 이 회사가 개발하고 있는 차세대 CPU 등에 채용되는 각종 기술을 공개했다.

이 가운데 Intel 상석 부사장 겸 Intel 아키텍처/그래픽 솔루션 사업 본부장 겸 에지 컴퓨팅 솔루션 주임 아키텍트 라자 코두리가 Intel이 개발하고 있는 새로운 CPU 마이크로 아키텍처의 개발 코드 네임이 "Sunny Cove"(서니 코브)인 것을 밝혔다.

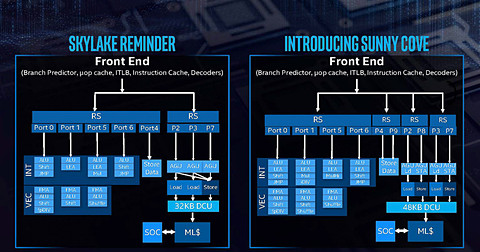

Sunny Cove는 2019년 말까지 발매되는 Xeon이나 Core 프로세서의 마이크로 아키텍처로서 채택된다. 현행 제품의 베이스가 되고 있는 Skylake와 비교해 Sunny Cove는 실행 포트가 8에서 10으로 증가되고 있는 것, L1 데이터 캐시가 32KB에서 48KB로 증가되고 있는 등의 확장이 더해지고 있어 Core 프로세서로서는 오랜만에 내부 아키텍처에 큰 개량이 추가된다.

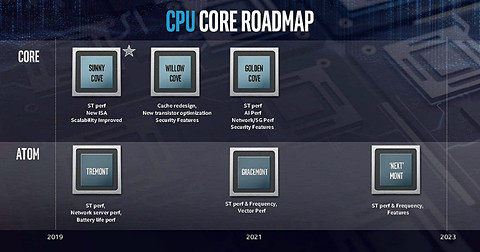

2019년에 투입되는 Xeon, Core 타겟 Sunny Cove, 그 후 Willow Cove, Golden Cove로 진화

기자 회견에서 코두리는 Intel이 개발하고 있는 CPU 마이크로 아키텍처(설계상의 사양)에 관한 설명으로 내년(2019년) 말까지 투입을 계획하고 있는 Xeon 프로세서, Core 프로세서의 CPU 마이크로 아키텍처의 개발 코드 네임이 "Sunny Cove"(서니 코브)인 것을 분명히 했다.

Sunny Cove는 Intel이 2020년에 Xeon 서버 전용으로 투입을 계획하는 "Ice Lake"에 채용될 예정인 것 외에 클라이언트 PC 전용에도 2019년에 투입될 계획이라고 설명했다.

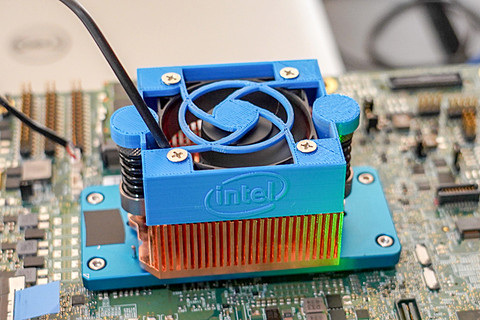

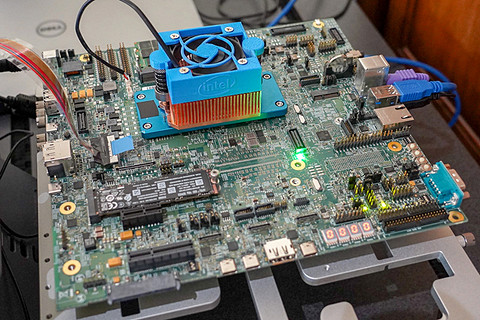

다만 현시점에서는 클라이언트 전용으로 어느 CPU에 탑재될 예정인지는 명확하게 되어 있지 않지만 Sunny Cove라고 여겨진 CPU가 탑재된 마더보드에는 "ICL" 등의 표시가 남아 있어 Ice Lake일 가능성이 높다.

코두리에 의하면 최초의 Sunny Cove 탑재 제품은 10nm 프로세스 룰로 제조될 예정이다.

코두리에 따르면 Intel은 우선 Sunny Cove를 투입하고, 그 뒤를 이어 캐시를 재 디자인해 새로운 트랜지스터에 최적화 된 개량판으로 Willow Cove(윌로우 코브), 2021년에는 성능을 끌어올린 Golden Cove(골든 코브)를 투입한다.

Atom 프로세서의 신코어도 계획되고 있는 것이 밝혀져 2019년에 성능을 향상시킨 네트워크/서버 전용 "Tremont(트레몬트), 2021년에 스칼라 성능, 주파수, 벡터 성능을 끌어올린 "Gracemont(그레이스몬트)", 또한 그 후에도 명칭은 미정인 "~mont" 라고 하는 코드 네임으로 차세대 제품을 계획하고 있다고 밝혔다.

Sunny Cove는 Skylake세대와 비교해 IPC가 크게 향상

Intel 펠로우 겸 Intel 아키텍처·그래픽스 솔루션 사업 본부 CPU 컴퓨팅 아키텍쳐 Intel 아키텍처 사업부 부장은 Sunny Cove 마이크로 아키텍쳐의 개요를 설명했다.

설명에 의하면 Sunny Cove는 IPC(사이클당 실행할 수 있는 명령수)를 향상시키는 개량이 진행되고 있어 클럭 주파수가 오르지 않아도 성능이 향상되는 설계를 목표로 하고 있다.

그는 개발코드 네임 Skylake(스카이레이크)와 Sunny Cove의 내부구조를 비교하며 Sunny Cove의 강화점을 설명했다.

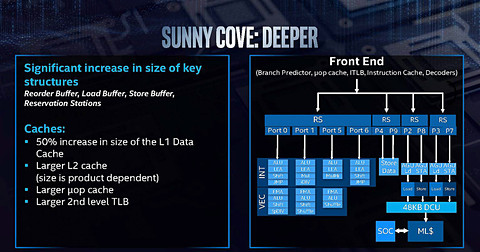

그것에 따르면 Sunny Cove는, 리오더 버퍼, 로드 버퍼, 스토어 버퍼, 리저베이션 스테이션(스케줄러) 등의 사이즈나 구조도 강화되고 있으며 특히 캐시는 L1 데이터 캐시가 50%(32KB에서 48KB로), L2 캐시 사이즈도 Skylake 세대보다 더 커지고 있다.

다만 L2캐시의 용량은 Skylake 세대에서 그랬듯이 제품에 따라 다르지만 "Xeon용 디자인은 보다 크고, 클라이언트용은 그것보다 작다는 것은 Skylake 세대와는 공통이지만 용량 그 자체는 양쪽 모두 Skylake 세대보다 커지고 있다"고 밝혔다.

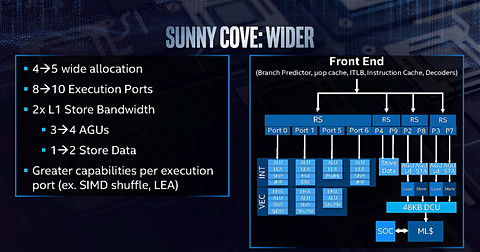

내부의 실행 유닛도 확장되어 Skylake 세대에 비해 와이드 어로케이션이 4에서 5로, 그리고 실행 포트는 8에서 10으로 늘어났다.

늘어난 실행포트는 AGU가 1개(3에서 4로)로, 스토어 데이터가 1개(1에서 2로) 늘어난다. 실행 포트의 몇 개에는 SIMD Shuffle, LEA 등의 기능이 추가되어 있다.

이를 통해 1클럭 사이클로 실행할 수 있는 명령수가 증가하고 있으며 병렬 실행시 효율을 올리고 있는 것이 Sunny Cove의 특징이 된다.

분기 예측 버퍼도 늘리고 있어 새로운 알고리즘을 도입해 정확성을 보다 향상시키는 등의 개량을 가하고 있는 등 효율성을 올리는 개선도 가해지고 있다.

새 명령세트도 도입될 예정이며 특히 암호화 관련 추가 명령세트(vector AESSHA-NI 등) 강화가 이뤄질 것으로 알려졌다. 전시회장에서는 오픈소스 압축·해제 소프트웨어인 7zip 소스 코드를 바꿔 Sunny Cove의 신명령 세트에 대응시킨 데모를 진행했는데 대응하지 않는 Kaby Lake로 실행했을 경우와 비교해 75% 고속으로 처리할 수 있었다.

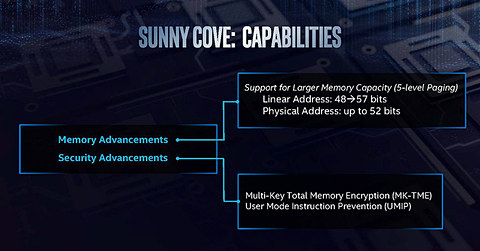

또 메모리 어드레스도 강화되고 있다. 주소 가능한 가상 메모리는 Skylake 세대의 48bit에서 57bit로 강화되고, 물리 메모리는 52bit로 확장된다. 이것에 의해 최대 4PB(페타바이트)까지의 물리 메모리에 대응하는 것이 가능하게 된다고 설명하고 있다.

'글로벌 IT 뉴스' 카테고리의 다른 글

| Arm 최초의 동시 멀티스레딩 대응 Cortex-A65AE CPU 발표 (0) | 2018.12.23 |

|---|---|

| 1TB/s 성능 초과 차세대 HBM 메모리 규격 업데이트 (0) | 2018.12.23 |

| 인텔, 업계 최초의 로직 3D 적층 패키징 기술 Foveros 발표 (0) | 2018.12.15 |

| Intel Architecture Day) 인텔의 차세대 아키텍처 기술 방향 (0) | 2018.12.15 |

| 차세대 DRAM(디램) 기술 (셀,셀렉터,채널,게이트,트랜지스터 등) (0) | 2018.12.15 |