인텔, 업계 최초의 로직 3D 적층 패키징 기술 Foveros 발표

미국 Intel는 11일(현지시간) Intel의 공동 창업자 로버트 노이스의 옛 사저에서 기자회견을 열고, 동사가 개발하고 있는 차세대 CPU 등에 채택되는 각종 기술을 공개했으며 Intel이 개발해 온 3D 다이적층 기술 "Foveros"를 발표했다.

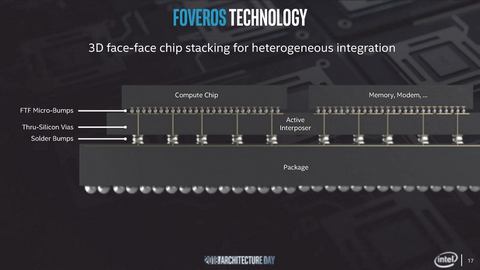

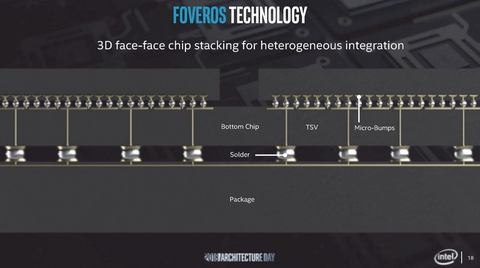

기존의 3D 다이적층은 CPU나 GPU 등의 로직 회로와 메모리 등을 3차원으로 적층하는 것이었는데 이번에 Intel이 발표한 Foveros는 메모리와 로직 뿐 아니라 논리적으로 로직과 로직을 3D로 적층하는 것이 가능해졌다. Intel에 따르면 로직간 3D 다이적층 기술은 업계 최초로 2019년에는 Foveros 기술을 채택한 최초의 x86 프로세서를 출시할 계획이다.

업계 최초의 로직과 로직을 3차원 적층하는 3D 패키징 기술 "Foveros"

Intel 상석 부사장 겸 Intel 아키텍처/그래픽스 솔루션 사업본부장 겸 에지 컴퓨팅 솔루션 아키텍트 라자 코두리는 "현재는 CPU, GPU, FPGA, 가속기 등 복수의 프로세서가 컴퓨팅 환경에서 이용되고 있는 헤테로지니어스 환경이 되고 있다. 그러한 가운데 패키징 기술의 진화, 특히 3차원 적층 기술이 요구되고 있었다"고 밝혔다.

그리고 코두리가 공개한 것은 "Foveros"라는 Intel이 개발 코드네임으로 부르고 있는 3D 패키징 기술이다. 3D 다이적층 자체는 지금까지도 GPU 위에 HBM 메모리를 적층하는 등의 형태로 이용되어 왔다. 그러나 로직과 로직을 적층하는 기술은 업계 최초이며 발열을 어떻게 해결하는지를 포함해 다양한 기술혁신을 포함시켰다.

Foveros는 Intel이 이미 투입한 Embedded Multi-die Interconnect Bridge(EMIB)라 불리는 2D 패키징 기술의 발전 기술이다. Intel은 개발코드 네임 "KBL-G" 등 여러 다이를 하나의 패키지로 통합하는 제품을 최근 추진하고 있으며 이번 3D 패키징 기술은 그 연장 선상에 있다.

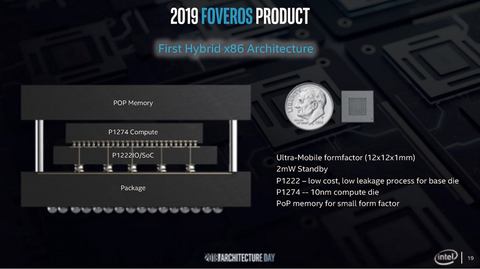

Intel에서는 이것을 2019년 후반에 실제 제품에 투입한다. 최초의 Foveros를 활용한 제품은 22nnm 프로세스 룰로 제조되는 SoC(x86 프로세서+I/O)에 10nm 프로세스 룰로 제조되는 것보다 강력한 처리 능력을 가진 x86 프로세서+GPU와 그 위에 메모리를 3단으로 겹친 제품.

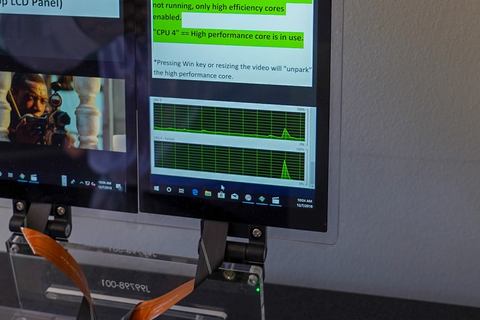

이번에 Intel은 그 최초의 제품을 실제로 가동한 데모를 공개했다. 현재의 엔지니어링 샘플에서는 팬이 필요하지만 실제 제품에서는 팬이 필요 없을 정도로 저전력이라고 밝혔다. 현시점에서는 이 Foveros에 대응한 제품이 어떠한 시장에 투입되는지 등에 관해서는 밝혀지지 않았다.

'글로벌 IT 뉴스' 카테고리의 다른 글

| 1TB/s 성능 초과 차세대 HBM 메모리 규격 업데이트 (0) | 2018.12.23 |

|---|---|

| 인텔, 차세대 CPU 아키텍처 서니코브, 윌로우 코브, 골든 코브 발표 (0) | 2018.12.15 |

| Intel Architecture Day) 인텔의 차세대 아키텍처 기술 방향 (0) | 2018.12.15 |

| 차세대 DRAM(디램) 기술 (셀,셀렉터,채널,게이트,트랜지스터 등) (0) | 2018.12.15 |

| ASUS, USB Type-C 게임 헤드셋 ROG Delta 발매 (0) | 2018.12.09 |