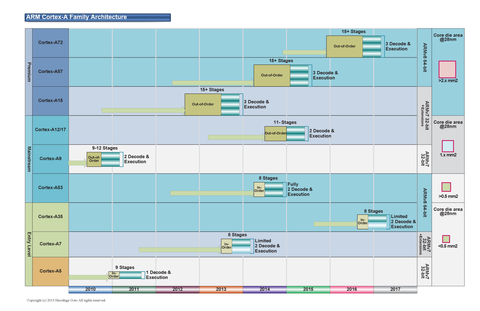

최소 0.45㎟로 작은 Cortex-A35 코어

ARM의 엔트리 수준의 64-bit CPU코어 "Cortex-A35"는 ARM의 CPU코어 전략의 변화를 상징한다. Cortex-A35의 마이크로 아키텍처와 다이면적을 다른 Cortex-A 패밀리와 비교하면 Cortex-A패밀리 전체의 변화가 보인다.

이번 Cortex-A35는 NEON유닛 없이 8KB L1의 최소 구성시 다이 영역이 0.4㎟다. ARM의 CPU코어는 보통 RTL로 소프트웨어 라이센스로 구성은 컨피규러블 되고 있다. 표준적인 구성은 L1이 32KB씩이며 NEON유닛도 갖추는데 최소 구성에서는 이들을 생략하고 그 밖에도 깎인 파라미터를 모두 최소화하고 있다. 그래서 표준 구성의 다이면적은 이보다 훨씬 커진다.

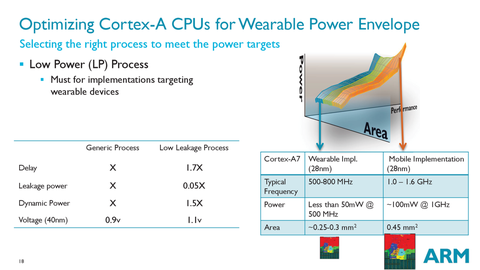

Cortex-A35의 앞 세대에 해당하는 Cortex-A7은 NEON유닛을 구현하는 32KB의 L1캐시 탑재의 보통 구성의 경우 28nm프로세스에서 0.45㎟의 다이사이즈라고 ARM은 밝혔다. 이 Cortex-A7을 최소 구성으로 NEON 유닛을 빼고 8KB의 L1으로 할 경우 코어 다이면적은 이 가운데 절반가량인 0.25~0.3㎟ 사이즈다. 같은 Cortex-A7에서도 보통 구성과 최소 구성에서는 다이 면적에 상당한 차이가 난다.

Cortex-A7의 구성에 의한 다이면적 차이

최소 구성의 크기를 비교하면 Cortex-A35는 Cortex-A7보다 33~60% 크다. 최소 구성으로 삭감되는 L1과 NEON유닛의 사이즈가 크게 다르지 않다고 하면 표준 구성의 Cortex-A35는 0.55~0.6㎟ 정도의 다이면적으로 보인다. 실제로는 부동 소수점 연산 유닛은 강화되고 있어 표준 구성이 커질 가능성이 있다. 그러나 설계와 프로세스의 성숙에 의한 다이 축소도 있으므로 다이 면적이 반드시 더 커지는 것은 아니다.

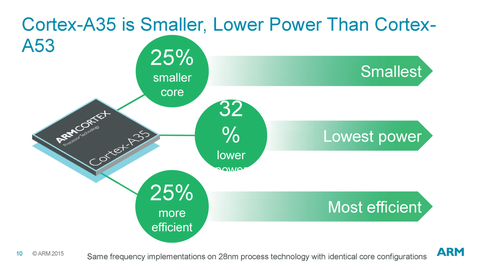

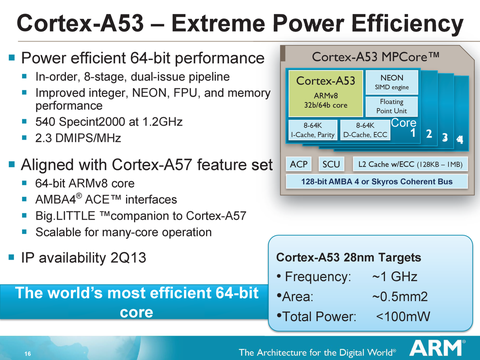

Cortex-A35를 같은 ARMv8-A 아키텍처의 Cortex-A53와 비교하면 파이프 라인 아키텍쳐는 같은 인 오더 실행에서 최대 2명령 디코드며 그런데도 Cortex-A53의 다이가 크다. 이는 Cortex-A53은 풀 2명령 디코딩인 반면 Cortex-A35는 매우 한정적인 2명령 디코딩에 아키텍처의 복잡도가 다르기 때문이다.

Cortex-A53의 타깃 다이 영역은 ARM의 발표때 28nm 프로세스에서 0.5㎟다. 그러나 실제 제품에서 표준 구성의 경우 그것보다 큰 사이즈의 실장이었다. 그리고 이번 Cortex-A35는 Cortex-A53 보다 25% 작은 다이면적으로 발표된 바 있다.역산하면 Cortex-A53은 표준 구성에서 0.7㎟ 클래스의 다이면적이다.

더구나 같은 28nm에서 같은 구성의 CPU 코어인데도 프로세스의 옵션이나 표준 셀 라이브러리의 셀 하이트의 차이에 의한 다이면적은 크게 다르다. 같은 구성의 CPU 코어에서도 성능을 중시하는 구현은 저전력 실장보다 최대 40~50% 정도 커진다. 그래서 ARM의 설명에 있는 다이 사이즈는 기준에 불과하지만 상대적인 지표는 된다.

복잡화되는 모바일 SoC에서 ARM CPU 코어 구성

Cortex-A35의 목적은 현재 ARMv7-A 명령 세트 아키텍처의 Cortex-A7이 사용되고 있는 엔트리 수준의 스마트폰 시장을 ARMv8-A 명령 세트의 Cortex-A35로 바꾸는 것, 또 Cortex-A72와 Cortex-A53으로 구성된 big.LITTLE 구성에 Cortex-A72와 Cortex-A35의 선택 사항을 펼칠 것이다. 복잡한 ARM의 CPU코어 구성을 ARMv8-A 64-bit 아키텍처에서 통일할 수 있겠다는 것이다.

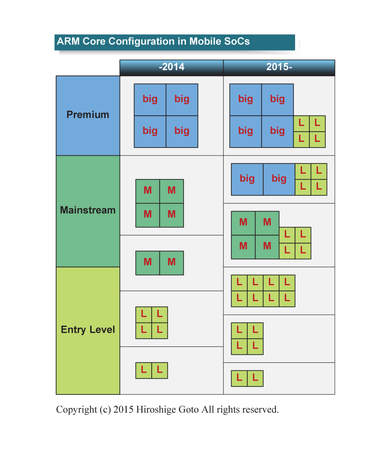

빅리틀(big.LITTLE)이 침투하기 전의 모바일 SoC에서 ARM의 ARMv7-A 명령 세트 CPU코어의 구성은 매우 간단한 것이었다. 하이엔드 SoC는 Cortex-A15 클래스의 대형 CPU의 쿼드 코어 구성이 주류고, 메인 스트림에서는 Cortex-A9 기반의 중형 CPU 코어로 쿼드 코어와 듀얼 코어가 주류, 엔트리급은 Cortex-A7급 소형 CPU코어로 쿼드 코어와 듀얼 코어를 사용했다. 물론 예외도 있지만 비교적 간단한 세계였다. 이는 코어가 클수록 성능이 높지만 전력 소비도 오른다는 트레이드 오프가 있었기 때문이다.

그런데 현재 모바일 SoC의 CPU 코어는 ARM 코어만 놓고도 매우 복잡해지고 있다. big.LITTLE에 의해서 코어 크기에 의한 저부하시 전력 소비가 줄어들게 됐기 때문이다.

현재의 ARM CPU 코어 모바일 제품의 구성은 big.LITTLE에 의해서 복잡해지고 있다

현재로서 하이엔드 주류는 4개의 빅 코어와 4개의 리틀 코어를 조합한 대형 코어와 소형 코어의 대칭 구성이다. 그러나 미들 레인지 제품에서는 2개의 대형 코어와 4개의 소형 코어의 조합이 확산되고 있다. ARM은 당초 중형 코어와 소형 코어의 조합이 메인 스트림으로 온다고 설명하고 있었지만 그러한 구성은 마이너로 머물고 있다.

이유는 몇가지 있다. 우선 대형 코어 2개와 중형 코어 4개를 비교하면 싱글 스레드 성능이라면 대형 코어쪽이 높은 것. 또 대형 코어가 필요한 작업은 2코어 정도로 커버할 수 있는 경우가 많다. 그래서 중형 코어 4개를 올리는 것 보다 대형 코어 2개 구성 쪽이 유리하다고 보는 듯하다.

또 64-bit의 ARMv8-A로 이행이 진행되는 가운데 ARMv8-A의 중형 코어가 제공되지 않은 것도 이유다. 64-bit를 요구하는 SoC 판매업자는 중형 코어를 선택할 수 없다. 무엇보다 ARM측은 ARMv8-A 세대에서는 메인 스트림에서는 대형 코어 2개+소형 코어 4개의 비대칭 big.LITTLE이 주류가 되기 때문에 중형 코어의 64-bit화의 니즈는 아직 낮다고 설명했다. 닭과 달걀 같은 관계지만 ARM은 현재 코어 구성에서 중형 코어는 32-bit에 두고 있다.

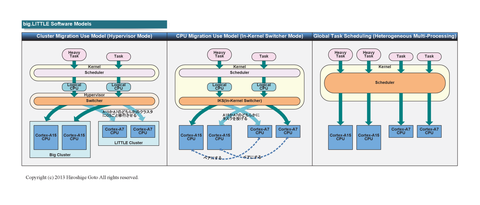

또 배경적인 이유로는 ARM의 big.LITTLE 제어 소프트웨어 기술이 발전한 측면도 있다. 옛 모델에서는 big.LITTLE의 big측과 LITTLE측에서 같은 CPU코어 개수일 필요가 있었다. 하지만 지금은 비대칭 CPU코어 수에서도 소프트웨어가 제어할 수 있다. 이는 대칭형 CPU코어로 구성하지 않아도 제어할 수 있는 소프트웨어 모델 "Global Task Scheduling(GTS)"가 제공됐기 때문이다. GTS가 촉발된 SoC 판매업자의 big.LITTLE에 대한 대응이 급속히 진행됐다.

중형 CPU 코어가 흐려지는 현재의 ARM Cortex-A 패밀리

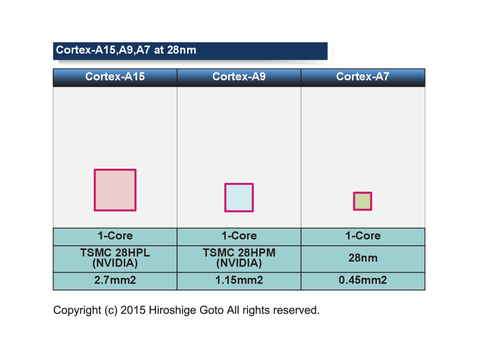

이런 상황에서 ARM의 Cortex-A 계열 CPU코어 전략은 미묘하게 변하고 있다. 종래의 ARM CPU코어는 소형 CPU코어와 대형 CPU코어의 2계열이었다. 대형 CPU코어는 소형 CPU코어에 비해 다이 지점에서 2~4배의 크기였다. 그러나 Cortex-A15의 등장으로 대형 CPU코어가 패밀리에 가세했다. 28nm 프로세스에서의 각 코어의 다이 지역의 상대적인 비교는 아래와 같다. NVIDIA의 Cortex-A15의 28HPL은 약간 큰 실장, Cortex-A7은 ARM 지표의 다이면적이다.

간단한 ARMv7 시대의 Cortex-A 패밀리의 다이 지역

간단히 말하면 Cortex-A 패밀리는 소형 CPU코어에 비해 중형 CPU코어는 2.x배, 중형 CPU코어에 비해 대형 CPU코어도 2.x두배 크기이다. 중형 CPU코어는 마침 대형 CPU코어와 소형 CPU코어의 중간에 끼어 알기 쉬운 상대적인 다이면적이었다. CPU코어는 마이크로 아키텍처적으로 대형 CPU코어는 3명령 디코딩의 아웃 오브 오더 실행, 중형 CPU코어는 2명령 디코딩의 아웃 오브 오더 실행, 소형 CPU코어는 2명령 디코딩의 인 오더 실행이 된다.

그런데 여기에 와서 big.LITTLE과 ARMv8-A에 의해서 중형 CPU코어의 존재가 모바일 SoC에서는 흐려졌다. 그래서 ARM은 CPU코어의 포지션을 처음부터 다시해 종래는 엔트리 레벨 전용의 소형 CPU코어인 Cortex-A53을 메인 스트림용이라고 포지션을 고쳤다. 그리고 엔트리 수준으로는 더 작은 다이면적의 Cortex-A35를 투입했다.

그래서 현 Cortex-A 패밀리의 CPU코어의 위상과 다이면적 관계는 이전과는 꽤 변했다. 프리미엄 Cortex-A57/72가 다이면적으로 최대의 28nm라면 2.x 제곱mm클래스. 이것은 종래대로지만 메인 스트림에 위치하고 있는 Cortex-A53은 28nm에서는 1㎟를 크게 자른다. 그리고 엔트리에 규정된 Cortex-A35에 Cortex-A53은 다이면적이 25% 증가에 지나지 않는다. 원래 소형 CPU코어인 Cortex-A53이 메인 스트림에 위치하고 있다.

기존의 중형 CPU코어가 ARMv8-A기반의 CPU코어는 없다

언뜻 봐서 알 수 있듯이 프리미엄 CPU코어와 메인 스트림 CPU코어의 다이면적 차이가 크고 메인 스트림과 엔트리의 차이가 작다. 원래 엔트리 수준이던 Cortex-A53을 메인 스트림으로 규정했기 때문에 이것도 당연하다. 이처럼 비용 구조에 영향을 줄 코어 영역과 코어 시장 위치는 종전과 달라지고 있다.

멀티 코어화에 따른 CPU코어의 크기를 축소

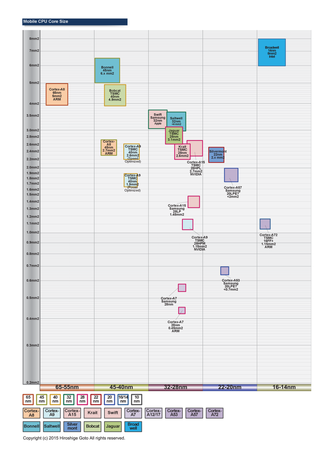

더 큰 변화는 CPU코어의 다이 지역 축소다. 65nm프로세스에서 Cortex-A8은 1개의 CPU코어가 5㎟였다. 그것이 40nm의 Cortex-A9이 되면서 코어의 사이즈는 2㎟ 안팎에서 2.6㎟ 정도로 축소. 대형 CPU코어인 Cortex-A15는 28nm프로세스에서 2.x제곱mm정도로 40nm의 Cortex-A9과 동등하게 진정되고, 다이 지역은 보합세를 보였다. 그것이 현재의 14/16nm프로세스는 대형 CPU코어인 Cortex-A72 조차 다이면적은 1㎟대로 축소되었다.

간단히 말하면 ARM의 최고 성능 CPU코어는 65nm에서 40nm로 절반 크기로 되어 40nm에서 28nm는 같은 수준, 그리고 28nm에서 14/16nm에서 더욱 절반 크기가 됐다. 프로세스의 미세화에 따른 코어를 대형화하기보다 코어를 축소하는 방향으로 향하고 있다.

ARM이 상대적으로 CPU코어 크기를 미세화와 함께 작게 하는 이유는 2가지다. 하나는 멀티 코어화, 다른 하나는 빅리틀(big.LITTLE)화다.

모바일 SoC의 성능 강화와 함께 CPU코어의 멀티 코어화가 진행되었다. Cortex-A9 세대가 되면서 듀얼 코어가 당연시되어 Cortex-A15가 되면서 쿼드 코어도 당연시됐다. 65nm의 Cortex-A8은 싱글 코어로 5㎟였지만 40nm의 Cortex-A9은 듀얼 코어에서 5~6.x제곱mm대의 사이즈이다. 여기에서는 미세화와 함께 CPU코어 수를 2배로 늘렸다.

Cortex-A15세대가 되면서 쿼드 코어가 일반화 되었다. 그 결과 28nm의 Cortex-A15 CPU코어 자체는 40nm의 Cortex-A9과 사이즈가 크게 변하지 않아도 CPU코어와 L2캐시 영역은 10㎟대 후반으로 급증했다. 28nm세대의 프리미엄 모바일 SoC는 다이중 CPU면적이 상대적으로 넓다.

20nm에서 14/16nm는 CPU코어를 축소하면서 쿼드 코어 CPU 영역의 면적이 줄고 있다. Cortex-A72의 ARM 지표의 구현은 16nm공정의 쿼드 코어에서 8㎟로 40nm시의 듀얼 코어 크기에 가깝다. ARM이 같은 차원의 면적에 더 많은 코어를 맞추려 CPU코어의 크기를 작게하고 있는 것을 알수 있다.

이에 박차를 가한 것은 big.LITTLE이다. big.LITTLE로 big의 대형 CPU코어 클러스터만 아니라 LITTLE의 소형 CPU코어의 클러스터도 탑재하게 됐다. 그만큼 CPU면적이 더해진다. ARMv8-A세대의 쿼드 코어 클러스터 사이즈로 비교하면 big의 Cortex-A57코어는 LITTLE의 Cortex-A53 코어의 2~3배. Cortex-A35는 LITTLE측의 CPU클러스터 사이즈를 조금이라도 줄인다는 효과가 있다.

ARM보다 아키텍처를 확장하는 아키텍처 라이센서

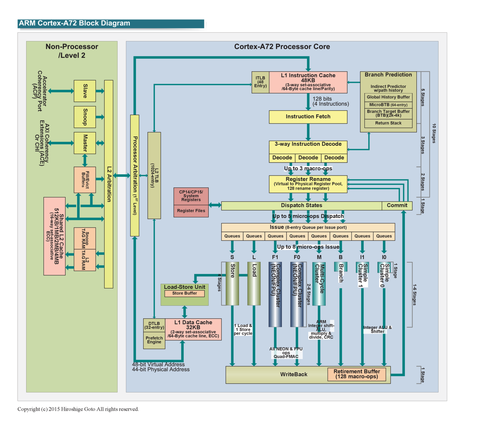

이렇게 보면 ARM은 일정 면적에 CPU코어 군의 다이면적을 억제하려하고 있으며 이를 위해 CPU코어의 면적을 작게 두고 있음을 추측할 수 있다. 그러나 그 때문에 ARM은 CPU코어 마이크로 아키텍처의 확장 속도를 늦추고 있다. Cortex-A15부터 Cortex-A72까지 ARM의 톱 CPU코어의 내부 아키텍처는 3명령 디코딩 베이스는 공통되고 있다. 다이면적으로도 소비 전력으로도 확장할 기회였던 14/16nm로 이행했지만 아직 확장하지 않고 있다.

이러한 ARM의 전략을 위해 ARM자체 IP의 CPU코어는 최근 싱글 스레드 성능을 내기보다는 멀티 쓰레드 성능을 올리는 방향으로 진행됐다. 싱글스레드 성능도 올리고 있는데 그것보다 코어 수를 늘리는 쪽에 중점이 있었다. 싱글 스레드 성능은 극적인 향상은 되고 있지 않다. 그래서 ARM의 아키텍처 라이센스를 받고 있는 칩 벤더는 ARMv8-A코어를 다른 방향으로 진화시키고 있다.

원래 ARM서버 계열에서는 아키텍처 라이센스를 받고 스레드당 성능을 올린 CPU코어가 개발됐지만 현재는 모바일에서도 그 경향이 강해지고 있다. 모바일로 독자적 CPU코어 개발 업체인 Apple이나 Qualcomm, NVIDIA는 모두 ARM 자체 IP코어보다 마이크로 아키텍처를 확장한 강력한 CPU코어를 개발하고 있다.

Apple은 iPhone 5의 A6 SoC에서 아키텍처 라이센스에 따른 독자 개발 CPU코어로 전환했다. Apple은 학회 등에서 CPU아키텍처의 발표를 일절 하지 않지만 LLVM의 리뷰에 이 회사의 CPU 마이크로 아키텍처의 데피니션이 기록되어 있다. 그것을 보면 명령 다중성을 높인 Apple코어의 윤곽을 알 수 있다. Apple의 코어는 1세대 전의 싸이클론(Cyclone, iPhone 6/iPhone 5s계열의 코어)에서 6마이크로 OPs(내부 명령)를 각 사이클에 처리할 능력이 있다. 정수 연산 파이프가 4개, 정수 곱셈 파이프가 1개, 나눗셈 파이프가 1개, 로드/스토어 파이프가 2개, 이 외에 분기 유닛이 2유닛과 간접 분기 유닛이 1. 정수 계열만 Cortex-A72의 2배 정도 넓은 파이프 구성이다.

Qualcomm이 Snapdragon 820에 탑재한 자사 개발 코어 Kryo는 아직 윤곽이 나타나지 않았지만 이쪽도 더 넓은 명령 디코딩&실행 대역을 갖는다고 알려졌다. NVIDIA의 Denver는 명령 디코더 자체는 2-way지만 일단 디코딩 한 명령에 최적화 스케줄링을 갖고 최대 7마이크로 OPs의 병렬 실행이 가능하다.

Apple, Qualcomm, NVIDIA등의 아키텍처 라이센스 CPU코어는 모두 ARM의 Cortex-A57/72코어보다 크기도 대형 코어가 된다. 즉, ARM이 CPU코어를 소형화하는 한편, 라이선스를 받은 업체는 ARM보다 사이즈가 큰 CPU코어를 만든다. 코어 크기의 계층적으로는 아키텍처 라이센스 코어, ARM의 대형 코어, 중형 코어, 소형 코어라는 4계층이 되고 있다.

다만 ARM이 CPU코어의 다이면적과 마이크로 아키텍처의 계층을 바꾼 것은 어쩌면, 향후 ARM이 CPU코어의 계층을 더욱 변화시키는 전조일지도 모른다.

14/16nm프로세스에서 Cortex-A72쿼드 코어 클러스터는 40nm의 듀얼 코어 클러스터 사이즈로 바짝 다가오고, 10nm세대에서 ARM은 CPU코어를 대형화 할 여유가 있다. ARM이 10nm프로세스를 겨냥하고 있는 차세대 CPU코어 Artemis(아르테미스)는 보다 복잡한 마이크로 아키텍처에 싱글 스레드 성능을 극적으로 높인 근원이 될지 모른다.

출처 - http://pc.watch.impress.co.jp/docs/column/kaigai/20151128_732643.html