6월 VLSI에서 인텔이 비트코인(Bitcoin) 마이닝 칩 발표

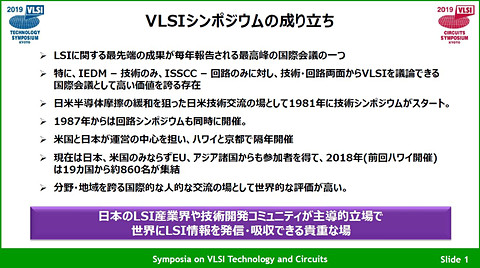

반도체 디바이스 기술과 반도체 회로 기술에 관한 최첨단 연구 성과를 과시하는 국제 학회 "VLSI 심포지엄(VLSI Symposia)"이 올해(2019년)도 6월에 개최된다.

VLSI 심포지엄 사무국은 보도 기관 전용 설명회를 도쿄에서 열고, 개요를 설명했다. 또, 공식 사이트에서 프로그램을 공표했다.

VLSI 심포지엄의 가장 큰 특징은 반도체 디바이스 기술에 관한 국제 학회 "Symposium on VLSI Technology(VLSI 기술 심포지엄)"과 반도체 회로 기술에 관한 국제 학회 "Symposium on VLSI Circuits(VLSI 회로 심포지엄)"으로 심포지엄 전체가 구성되어 있는 점에 있다. VLSI 심포지엄(VLSI Symposia)은 전체의 총칭이다.

VLSI 기술 심포지엄과 VLSI 회로 심포지엄은 쌍이 되어 같은 기일, 같은 회장에서 개최된다. 참가자 등록은 어느 쪽의 심포지엄이 되지만 참가자는 양쪽 모두의 심포지엄을 들을 수 있다. 또 양 심포지엄 합동 세션이 몇 가지 준비되어 있다.

즉, 반도체의 디바이스 기술과 회로 기술, 또 프로세스 기술과 시스템 기술에 관한 최신 기술 동향을 참가자가 입수할 수 있다. 반도체 기술 국제학회에서 이와 같이 폭넓은 분야를 커버하고 있는 것은 아마 유례가 없을 것이다.

VLSI 심포지엄의 또 한가지 특징은 일본과 미국에서 번갈아 개최하고 있다는 점이 있다. 근년은 서기 홀수년에 일본의 교토, 짝수년에 미국 하와이에서 개최하는 것이 통례다. 올해는 서기 홀수년이므로 교토에서 개최된다. 일본에서 열리는 반도체 기술 국제학회에선 VLSI 심포지움이 최대 규모일 것이다.

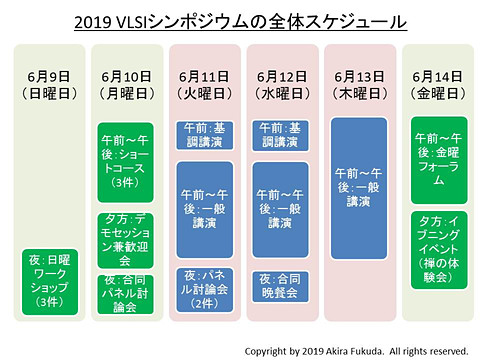

개최 기간은 2019년 6월 9일(일요일)부터 같은 해 6월 14일(금요일)까지 6일로 좌중은 교토시의 호텔 "리가 로열 호텔 교토". 교토 개최 장소로서 최근에 계속 사용되고 있는 호텔이다.

하루 기술 강좌와 3일 간의 기술 강연회, 하루 포럼으로 구성

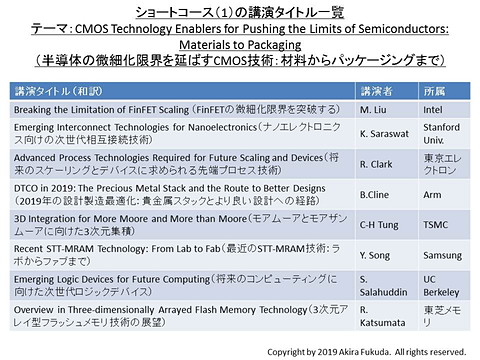

VLSI 2019의 일정을 조금 설명한다. 6월 9일(일요일)~14일(금요일)에서 11일~13일까지 메인 행사인 기술 강연 세션(테크니컬 컨퍼런스) 개최일. 메인 이벤트 전날 10일은 "쇼트 코스"라고 부르는 기술 강좌, 메인 행사 다음 날인 14일은 "포럼" 혹은 "금요일 포럼" 이라고 부르는 강연회다. "쇼트 코스"에서는 공통의 주제에 근거한 8개 안팎의 강의를 하루 만에 수강할 수 있다. 최근의 주제를 배울 수 있는 중요한 기회이며 "금요일 포럼"에서는 이것도 최근의 주제에 관한 5개 안팎의 강연이 예정된다.

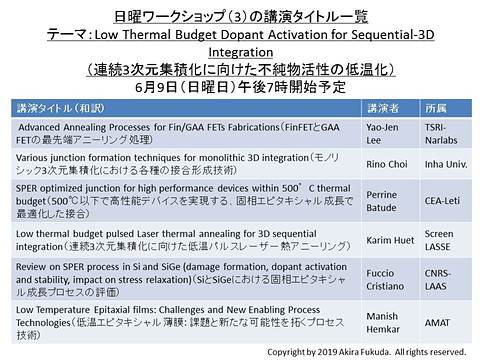

또 올해(2019년)은 9일 밤에 "워크숍" 혹은 "일요일 워크숍" 이라고 부르는 강연회가 새로 생겨났다. "워크숍" 에서는 VLSI 심포지엄의 기술 강연에서 커버하고 있지 않는 테마를 취급한다.

강연 이외의 이벤트에 대해서도 언급한다. 10일 밤에는 "시연 세션" 이라고 부르는 테이블 톱 형태의 미니 전시회와 리셉션(환영회), 또 두 심포지엄 합동 패널 토론회(패널 토론)가 개최된다.

11일 밤에는 2건의 패널 토론회가 예정되어 있다. 이 패널 토론회는 한건이 VLSI 기술 심포지엄, 다른 한건이 VLSI 회로 심포지엄이 주최한다. 또 12일 밤에는 두 심포지엄 합동 만찬(연회)가 개최된다.

흥미로웠던 것은 14일 "금요일 포럼" 의 뒤로 예정된 이벤트다. "이브닝 이벤트" 라고 칭하는 체험회가 개최된다.

가상현실, 증강현실, 양자 컴퓨터가 기조강연의 테마

VLSI 심포지엄의 메인 이벤트인 테크니컬 컨퍼런스(기술 강연회)의 개요를 소개한다.

예년과 마찬가지로 컨퍼런스는 기조 강연 세션에서 시작된다. 4건의 초청 강연이 예정되며 다만 지난해(2018년)까지 회의 첫날 오전에 4건 모두 기조 강연을 실시한 반면 올해(2019년)는 회의 첫날(6월 11일) 오전 2건, 컨퍼런스 2일째(6월 12일) 오전 2건으로 나누고 있다.

6월 11일 기조 강연 세션에서는 먼저 도쿄 대학의 이나미 마사히코 교수가 "Virtual Cyborg:Beyond Human Limits(가상 사이보그:인류의 한계를 넘어)" 의 타이틀로 가상 현실 기술과 증강 현실 기술, 로봇 기술을 기반으로 한 신체의 확장과 감각 및 정신의 변용에 대해서 설명한다.

이어 미국 DARPA(국방고등연구계획국)의 W.Chappel 씨가 'Managing Moore's Inflection: DARPA's Electronics Resurgence Initiative(무어의 변곡점을 제어: DARPA의 일렉트로닉스 재흥 계획)' 이란 타이틀로 강연한다. DARPA는 일렉트로닉스 기술의 50년 앞을 겨냥한 연구 프로젝트 "Electronics Resurgence Initiative(ERI)"의 개발을 재작년(2017년) 6월에 발표했다. 강연에서는 ERI의 목적이나 스케줄, 조직 구성, 현황 등이 이야기 될 것으로 보인다.

6월 12일의 기조 강연 세션에서는 Facebook의 S.Rabii 씨가 "Computational and Technology Directions for Augmented Reality Systems(증강 현실 시스템을 위한 컴퓨터와 테크놀로지의 방향성)" 을 주제로 강연한다. 현실의 세계와 가상의 세계를 융합시킨 증강 현실 시스템(AR시스템)의 보급에는 저전력 컴퓨팅 기술이 필수적이다. 이를 위한 요소 기술인 데이터 전송의 소비전력을 최소화하는 기술이나 고효율 프로그래머블 액셀러레이터 기술, 차세대 비휘발성 메모리 기술 등을 설명한다.

이어 도쿄대학 및 이화학 연구소에 소속된 다루다 세이고 씨가 "Si Platform for Developing Spin-Based Quantum Computing(스핀베이스의 양자 컴퓨팅 개발용 실리콘 플랫폼)" 이라는 타이틀로 강연한다. 실리콘의 전자 스핀에 의한 양자점을 사용한 계산 아키텍처 이점을 기술하고, 연구개발의 현황을 설명한다.

5G 대응 모바일 SoC가 채용한 CMOS 플랫폼 기술

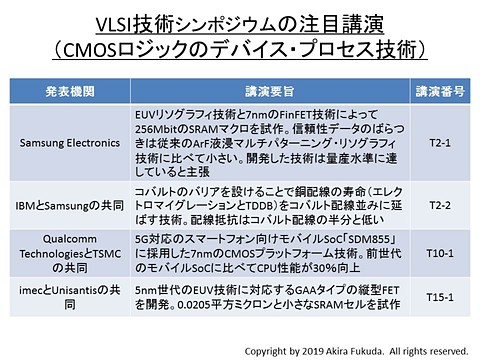

그러면 VLSI 기술 심포지엄과 VLSI 회로 심포지엄에서 주목해야 할 기술 강연을 소개한다. 처음은 VLSI 기술 심포지엄의 CMOS 로직 디바이스·프로세스 기술에 관한 강연이다.

Samsung Electronics(이하 Samsung)은 EUV 리소그래피 기술과 7nm세대의 FinFET 기술에 의해 256Mbit의 SRAM 매크로를 개발한 결과를 발표한다(강연 번호 T2-1). 종래의 ArF 액침노광과 멀티패터닝을 조합한 리소그래피 기술에 비하면 신뢰성 데이터의 격차가 작다. 개발한 기술은 양산 수준에 달했다고 한다.

IBM과 Samsung은 코발트 금속의 얇은 장벽 층을 만든 것에 구리 금속 배선의 수명(일렉트로 마이그레이션 수명과 TDDB 수명)을 코발트 금속 배선 수준으로 늘리는 기술을 공동으로 개발했다.(강연 번호 T2-2). 개발된 배선의 저항은 코발트 배선의 절반으로 낮다.

Qualcomm Technologies와 TSMC는 5G 대응 스마트폰 모바일 SoC "SDM855"에 채용한 7nm세대의 CMOS 플랫폼 기술을 공개한다.(강연 번호 T10-1) 앞선 세대의 모바일 SoC에 비해서 CPU의 성능이 30% 향상됐다.

3차원 교차점 구조에서 초 대용량 메모리를 목표로 한다

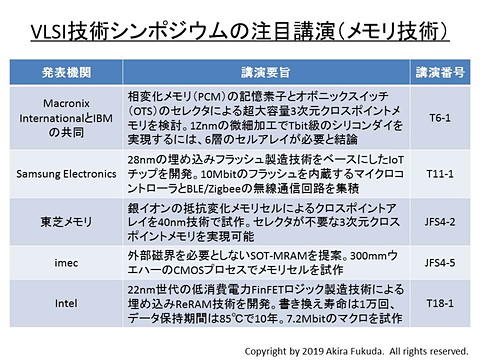

계속해서 VLSI 기술 심포지엄의 메모리 기술에 관한 주목 강연을 소개한다.

Macronix International과 IBM의 공동 연구 팀은 상변화 메모리(PCM)의 기억 소자와 오보닉 스위치(OTS)의 실렉터의 초 대용량 3차원 크로스 포인트 메모리를 검토한 결과를 공표한다.(강연 번호 T6-1) 1Znm세대의 미세 가공에서 Tbit 급의 실리콘 다이를 실현하려면 6층의 셀 배열이 필요하다고 결론지었다.

도시바 메모리는 은이온의 저항 변화 메모리 셀에 의한 크로스 포인트 구조의 메모리 셀 배열을 40nm 제조 기술로 개발했다.(강연 번호 JFS4-2)

카본 나노튜브에 있는 CMOS 로직과 CMOS 메모리

차세대 재료로서 기대되는 카본 나노 튜브(CNT)를 사용한 디바이스 기술의 발표에도 주목하고 싶다.

Massachusetts Institute of Technology(MIT)에서 2건의 성과 발표가 있다. 한건은 실리콘 광다이오드의 이미지 센서에 백 엔드 오브 라인(BEOL)의 프로세스에 의해 카본 나노 튜브(CNT)FET의 CMOS 회로를 단일 결정으로 적층 한 칩이다.(강연 번호 T2-5) CNT FET의 CMOS 회로에 의해 촬영 화상의 엣지를 리얼타임으로 검출한다.

다른 한건은 카본 나노 튜브(CNT)FET의 CMOS 회로에 의해 1Kbit의 SRAM을 개발한 결과 발표다.(강연 번호 T5-4) 1024개의 모든 메모리 셀들이 정상으로 동작했다.

이밖에 VLSI 기술 심포지엄에서는 TSMC가 발표 예정인 3차원 집적화 기술이 흥미롭다.(강연 번호 T2-3) 프론트 엔드 오브 라인(FEOL)의 프로세스에서 다른 실리콘 다이를 3차원 적층 한다. 실리콘 관통 전극(TSV) 기술이나 마이크로 범프 기술 등의 BEOL 공정 또는 패키지 공정에 의해 실리콘 다이를 3차원 적층 하는 방법에 비하면 실리콘 다이간 접속 대역 밀도와 전력 효율이 향상된다.

36칩을 접속한 DNN 액셀러레이터를 NVIDIA가 개발

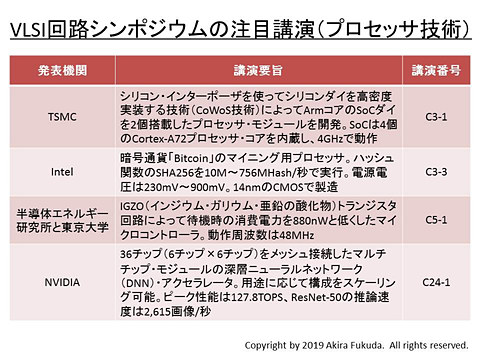

여기서는 VLSI 회로 심포지엄의 주요 강연을 본다. 처음은 프로세서 기술에 관한 강연이다.

TSMC는 실리콘 인터포저를 사용해 실리콘 다이를 고밀도로 실장 하는 기술(CoWoS기술)에 의해 Arm코어의 SoC 다이를 2개 탑재한 고성능 처리기 모듈을 개발했다.(강연 번호 C3-1) SoC는 4개의 Cortex-A72 프로세서 코어를 내장하고 4GHz로 동작한다.

인텔은 암호화폐 "비트코인(Bitcoin)" 마이닝용 프로세서를 발표한다.(강연 번호 C3-3) 해시 함수 SHA256을 10M~756MHash/s로 실행하며 전원 전압은 230mV~900mV. 14nm의 CMOS에서 제조했으며 실리콘 다이 면적은 0.15mm2.

NVIDIA는 36칩(6칩×6칩)을 접속한 멀티 칩 모듈 구성의 심층 뉴럴 네트워크(DNN)·액셀러레이터를 개발했다.(강연 번호 C24-1) 용도에 따라서 스케일링이 가능하며 피크 성능은 127.8TOPS, ResNet-50의 추론 속도는 매초 2,615.

출처 - https://pc.watch.impress.co.jp/docs/column/semicon/1182340.html

'글로벌 IT 뉴스' 카테고리의 다른 글

| AMD 실적 발표, 채굴 효과가 끝난 실제 실력은? (0) | 2019.05.01 |

|---|---|

| 마이크론, 엔터프라이즈 고용량 SSD 'Micron 9300 시리즈' 발표 (0) | 2019.04.27 |

| 인텔, 2.4Gbps 무선랜 Wi-Fi 6 모듈 출하 시작 (0) | 2019.04.27 |

| EIZO, USB PD 60W 대응 27형 ColorEdge CS2731 발매 (0) | 2019.04.27 |

| TSMC, 7나노 대비 18% 향상 된 6나노 프로세스 N6 발표 (0) | 2019.04.27 |