엔비디아 파스칼 아키텍처, 혁신적인 GPU의 이정표

NVIDIA CEO 젠슨 황

GTC에서 젠슨황 CEO가 파스칼을 대대적으로 발표

NVIDIA가 주최하는 GPU 컴퓨팅 컨퍼런스 "GPU Technology Conference(GTC)"에서 엔비디아는 차세대 GPU 아키텍처 "Pascal(파스칼)" 베이스의 GPU를 공식 발표했다. 이번에 발표된 것은 HPC(High Performance Computing)/서버용 하이엔드 GPU "테슬라 P100(GP100)". 앞선 세대의 Maxwell(맥스웰)은 하위 GPU부터 발표됐지만 이번 파스칼은 최상위 GPU부터 도입된다.

GTC의 기조 강연에서 NVIDIA의 젠슨황 CEO는 파스칼의 5가지 기술 포인트를 강조했다.

- 파스칼 아키텍처

- 16나노 FinFET 3D 트랜지스터 프로세스

- 실리콘 인터포저를 사용한 HBM2 메모리 기술

- 프로세서 간 접속의 NVLink

- 새로운 AI 알고리즘

마지막 AI 알고리즘은 GPU 측의 아키텍처 확장 결과에 의해서 실현되는 것이므로 파스칼 자체의 기술 혁신은 4가지다. 후술 하지만 사실은 파스칼의 중요한 특징은 최초의 GPU 마이크로 아키텍처 쇄신이다. 지금까지와는 방향을 바꾸어 GPU의 실효 성능을 올리는 방향으로 마이크로 아키텍처가 크게 확장됐다.

두번째의 프로세스 기술 혁신도 중요하다. 종래의 28nm 평면 트랜지스터 프로세스에서 16나노 핀펫 3D 트랜지스터 프로세스로 누설 전류(Leakage)가 크게 억제되어 전력 효율이 높아졌기 때문이다. HBM2 메모리는 720GB/sec(가까운 장래에는 1TB/sec)초 광대역을 실현한다.

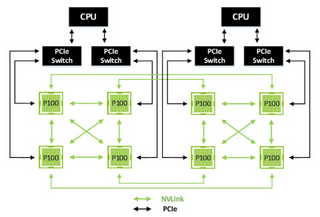

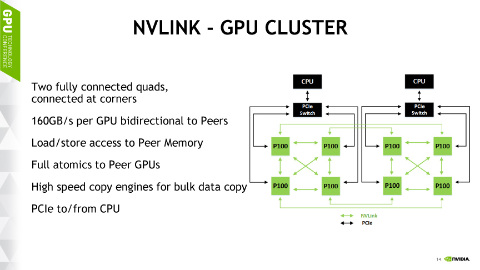

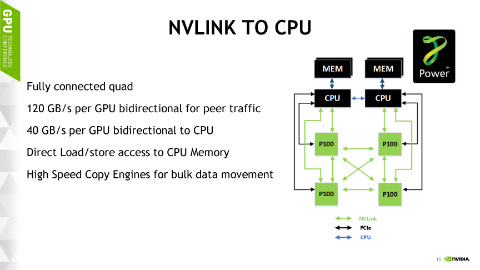

또 NVLink는 GPU 간을 40GB/sec의 링크로 직접 접속함으로써 GPU의 확장성을 극적으로 향상시킨다. GP100은 NVLink를 4링크로 준비해 8 GPU까지 2홉에 접속할 수 있다. 지금까지는 2GPU 구성이 일반적인 최대 규모의 노드에서 파스칼에는 8GPU 구성까지 확장된다.

이처럼 파스칼에서는 GPU 자체의 성능을 올릴 뿐 아니라 멀티 GPU 구성을 용이하게 하는 것으로 멀티 GPU에 의해 컴퓨트 노드당 성능을 극적으로 끌어올릴 수 있다. 덧붙여 IBM과 OpenPOWER의 Power 아키텍처 CPU도 NVLink를 지원하기 위해 NVLink GPU를 CPU에 직결할 수도 있다.

이렇게 열거하면 이번 파스칼이 NVIDIA GPU에 있어서 기술적으로 매우 큰 점프인 것으로 보인다. 프로세스 기술, 마이크로 아키텍처, 메모리와 패키징, 인터 커넥트 기술로 근본적인 기술 혁신이 빚어지고 있다. 점진적인 확장이었던 맥스웰과는 크게 다르며 그 전의 Kepler의 혁신보다 임펙트가 훨씬 크다.

NVIDIA GPU에 있어서 혁신 아키텍처가 파스칼이다. 또 향후 10nm 세대로 보이는 Volta(볼타)등 GPU는 이 파스칼의 연장선에 있을 것으로 추측된다. 그런 의미에서 앞으로 몇 세대의 NVIDIA GPU의 초석이 되는 GPU라고 할만하다.

FinFET 프로세스에 의해 동작 주파수와 성능을 끌어올린다

파스칼은 NVIDIA에게 FinFET 프로세스의 첫 외장 GPU다. 프로세스 노드의 숫자가 16이므로 제조원이 TSMC 인 것으로 나타났다. 트랜지스터가 누설 전류(Leakage)가 적은 FinFET이 되면서 전력당 성능이 오른다. 실제로 작동 주파수는 베이스가 Maxwell기반의 Tesla 948MHz에 비해 파스칼 베이스 Tesla는 1,328MHz로 크게 오르고 있다. 이는 전력을 절감함에 따른 주파수 향상의 여지가 생성됐기 때문이다.

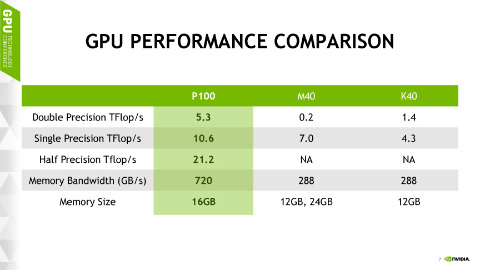

또, 프로세스가 미세화 되면서 다이당 트랜지스터 수는 앞 세대 Maxwell의 최대 구성인 GM200의 8B(80억 트랜지스터)에서 15.3B(153억)으로 1.91배로 거의 배증됐다. 다이 사이즈(반도체 본체의 면적)은 거의 같은 610mm2(GM200은 601mm2)이므로 트랜지스터 밀도가 1.88배가 됐다. 동작 주파수가 올랐고 트랜지스터 수가 늘면서 연산 성능도 증가했다. 앞선 세대의 Tesla M40(GM200)과 비교하면 단정밀도(32-bit) 부동 소수점 연산 성능은 7TFLOPS에서 10.6TFLOPS로 1.5배로 향상됐다.

그러나 파스칼 아키텍처의 특징은 이러한 기존의 GPU의 FLOPS 경쟁 이외의 부분에 있다. 파스칼에서는 단순히 단정밀도(32-bit:FP32) 성능 향상 뿐 아니라 메모리 대역 레지스터 수와 기내 쓰레드 수, 배정밀도(64-bit:FP64)와 반정밀도(16-bit:FP16) 부동 소수점 연산 성능을 대폭 높인 점이다. 한마디로 기존 GPU의 성능 경쟁과는 다른 스펙이 파스칼에서는 강화되고 있다.

FP32의 피크 성능 이외의 부분을 크게 확장

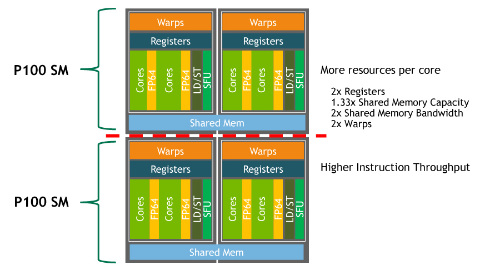

파스칼에서는 앞 세대 Maxwell에 비해 메모리 대역은 3배인 720GB/sec에 레지스터 수와 스레드 수는 2배로 공유 메모리는 1.3배, 배정밀도(FP64) 성능은 25배, 반정밀도(FP16) 성능은 3배인 21.1TFLOPS가 됐다. FP16의 20TFLOPS까지도 경이적이지만 FP64도 단번에 5.3TFLOPS가 된 실용적인 성능이 됐다.

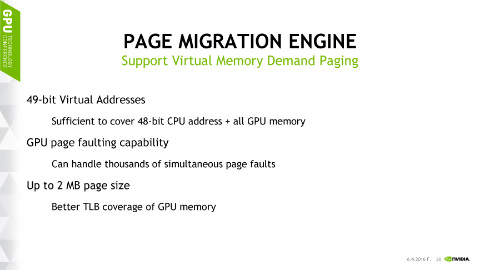

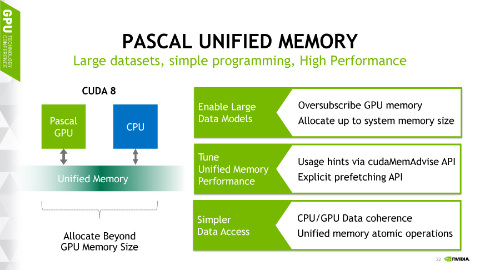

또 파스칼에서는 CPU와 메모리 공유 통합 가상 메모리 구조를 개선(GPU의 가상 메모리 공간을 확장하는 페이지 폴트의 지원 페이지 크기를 CPU에 맞춘) 콘텍스트 스위치 기능을 구현하고 GPU 간의 광대역 인터 커넥트를 갖춘 것도 특징이다. GPU 간을 직접 접속하는 NVLink에 의해서 GPU 간 대역은 5배로 직접 접속할 수 있는 GPU는 8개이며 제약이 강한 GPU의 확장성이 크게 향상됐다.

한마디로 마케팅적으로 영향이 있는 FP32 FLOPS 수의 배증에 연연하지 않고 프로세서로서 실효 성능의 향상에 주력한 것이 파스칼 아키텍처다. 프로세스의 미세화와 트랜지스터 수의 배증을 감안하면 NVIDIA는 파스칼 세대에서 단정밀도(FP32) 연산 유닛을 배가시키고 15TFLOPS의 GPU를 만들 수 있었다. 그러나 NVIDIA는 단정밀도 유닛은 죽이고, GPU를 효율적으로 가동시키는 기능에 늘어난 자원을 할애했다. 그래서 파스칼은 겉보기 스펙 이상으로 효율 성능이 높은 프로세서가 될 것으로 보인다.

구체적으로는 메모리 대역 확장으로 메모리 스톨이 줄어들 뿐 아니라 기내 쓰레드 수의 증대로 메모리 레이턴시가 향상되어 이 점에서도 GPU 가동률이 오른다. FP16(반정밀도)연산의 도입에 의해 FP16시의 효율 향상, GPU 사이의 데이터 교환의 효율도 올라간다. 지난 수세대 GPU에서 문제였던 GPU의 실효 성능 문제가 대폭 경감된다. FP16과 FP64의 성능은 두 정밀도를 필요로 하는 어플리케이션의 성능을 향상시킨다. 그 중에는 FP16 이용이 트렌드가 되는 딥러닝도 포함된다.

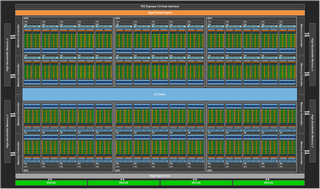

60개의 SM을 배치한 거대한 GPU 구성

Tesla P100(GP100)의 전체 구성은 아래의 그림과 같다. GPU 전체에서 총 60개의 SM(Streaming Multiprocessor)이 배치되고 있다. 제품 SKU는 60개의 SM 중 4개가 무효화되고 56개의 SM 구성으로 출하된다. 이는 610mm2의 대형 다이의 경우에는 다이 위에 흠이 있어 불량 코어가 발생할 확률이 높기 때문이다. 불량 SM을 무효화하는 용장성을 갖게 함으로써 제품 수율을 올릴 수 있다.

메모리 컨트롤러는 그림에서는 합계 8단위. 2유닛씩 1개의 HBM2 모듈에 연결된다. 각 메모리 컨트롤러가 512-bit 너비의 메모리를 제어한다. 오프 칩의 프로세서 간 인터 커넥트 NVLink는 그림 아래에 배치되고 있다. GP100은 4링크 구성되어 최대 4개의 GPU 또는 CPU와 직접 커넥트 할 수 있다.

중앙에 그려진 것은 L2 캐시로 이것도 Maxwell의 3MB에서 4MB로 늘리고 있다. L2는 실제로 메모리 컨트롤러에 가까이 배치되고 있는 것으로 보인다. 그림 위에 그려진 것은 PCI Express gen3 인터 커넥트와 GPU 전체 스레드 발행을 총괄하는 쓰레드 엔진이다.

60개의 SM은 10개씩 GPC(Graphics Processing Cluster)를 구성하고 있다. GPC는 말하자면 GPU 안의 미니 GPU로 GPU의 실행 파이프의 대부분을 포함, GPC는 GPU 전체에서 6개다. 파스칼 GP100의 GPC 수는 사실 Maxell GM200과 같다. 그러나 SM의 수는 GM200의 24개에 비해 GP100은 60개(유효화되는 것은 56개)러 크게 늘고 있다. 이것은 각각의 SM 구성이 작아졌기 때문이다.

SM구성을 Maxwell의 절반으로 변경

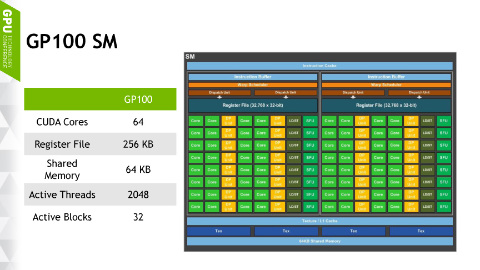

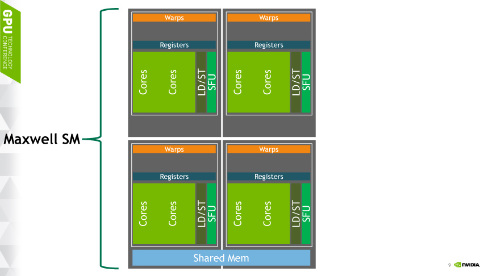

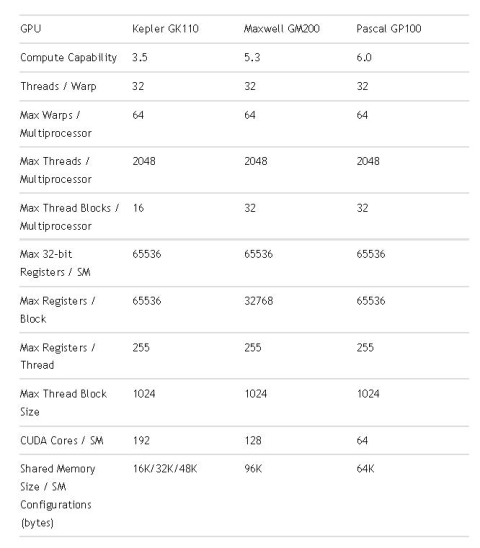

맥스웰과 파스칼은 SM 구성이 다르다. 핵심 CUDA 코어(FP32 부동 소수점 연산 프로세서)는 Maxell이 각 SM에 128개인데 파스칼은 64개다. 파스칼에서 1개의 SM이 크게 2개 블록으로 분할되며 각각 Warp 스케줄러 듀얼 명령 발행 유닛이 있다. 2개의 처리 블록은 각각 개별 Warp 배치를 수행하고 연산 유닛군으로 로드/스토어 유닛, 레지스터도 유닛으로 나뉜다.

그러나 텍스처 유닛과 텍스처/L1, 메모리는 2처리 블록에서 공유된다. 참고로 SM 당 64 FP32유닛의 구성은 AMD의 GCN(Graphics Core Next) 아키텍처의 CU(Compute Unit)와 같지만 내부 구성은 크게 다르다.

SM구성을 Maxwell과 비교하면 Maxwell에서는 SM이 4개의 처리 블록으로 구성되어 있었다. 파스칼과 마찬가지로 개개의 유닛이 개별적으로 명령 유닛과 연산 유닛, 레지스터를 가진 구조다. 파스칼의 SM 설계는 이 Maxell SM을 2개로 분할하는데서 시작됐다고 한다. 2처리 블록씩 2개의 SM으로 분할, 절반의 연산 유닛 수가 된 SM에 공유 자원을 각각 배정했다.

그 위에서 파스칼은 각 처리 블록의 자원을 대폭 강화했다. 자세한 건 나중에 리포트하겠지만 레지스터는 Maxwell이 각 블록 64KB(32-bit 레지스터 ×16,384)였다. 그것이 파스칼은 배가된 128KB(32-bit 레지스터 ×32,768)이다. 이는 GPU 연산 코어의 가동 효율에 큰 영향을 미치는 확장이다.

블록당 기내 설립 쓰레드 수가 2배로

GPU는 통상의 CPU처럼 쓰레드 당 레지스터 수의 할당은 고정되지 않았다. 드라이버의 컴파일러가 스레드에 물리적인 레지스터 수를 할당한다. NVIDIA GPU의 쓰레드당 최대 레지스터 수는 현재 255다. 그러나 GPU가 갖춘 물리적인 레지스터 수는 정해졌기 때문에 스레드당 레지스터 수와 세울 수 있는 스레드 수에는 트레이드 오프가 생긴다. 구성 쓰레드 수가 늘어나면 1스레드가 사용할 수 있는 레지스터 수가 줄어든다.

NVIDIA GPU는 32쓰레드씩 묶은 스레드 배치 "Warp"를 프로세서로 실행 단위로 하고 있다. NVIDIA GPU는 프로세서 클러스터 SM 마다 Warp를 제어하고 있다. SM에서 몇개까지 Warp를 만들 수 있는지는 GPU 아키텍처 세대마다 다르다. 레지스터 자원이 적으면 레지스터 할당의 제약 "레지스터 압박(Register Pressure)"으로 구성될 Warp가 줄고, 스톨이 생긴다.

파스칼은 레지스터 자원을 2배로 늘렸다. 그래서 같은 레지스터 할당의 경우 블록마다 세울 수 있는 쓰레드 수/Warp 수가 배로 증가하였다. Maxwell에서는 4블록으로 구성하는 SM 전체에 세울 수 있는 최대 Warp수는 64에서 쓰레드 수는 2,048이었다. 그것에 비해 절반의 2블록으로 구성하는 파스칼의 SM은 64Warp로 2,048스레드다. 블록당 쓰레드 수/Warp수는 2배가 되었다.

GPU는 방대한 스레드의 병렬화로 메모리 레이턴시를 억제하고 있다. 파스칼은 메모리 대역이 3배로 오르면서 경쟁에 의한 메모리 레이턴시의 증대를 억제하고 있다. 또 기내 스레드 수를 배증시킴으로써 레이턴시의 억제를 용이하게 하고 있다. 결과적으로 파스칼 아키텍처에서 SM의 가동률이 매우 향상될 것으로 예상된다.

파스칼의 SM은 레지스터/스레드 방향 외에도 크게 확장되고 있다. 그 부분은 다음 기사에 리포트 한다.

출처 - http://pc.watch.impress.co.jp/docs/column/kaigai/20160406_751980.html

'글로벌 IT 뉴스' 카테고리의 다른 글

| 엔비디아 드라이브PX2, 로봇 자동차 경주에 제공 (0) | 2016.04.11 |

|---|---|

| 인텔, 알테라의 FPGA "Arria 10 GX"를 통합한 Xeon 발표 (0) | 2016.04.08 |

| 인텔 틱톡 전략 변경, 새로운 3번째 단계 Optimization 추가 (0) | 2016.04.01 |

| 윈도우에 우분투 Bash 지원, 마이크로소프트 Build 2016 (0) | 2016.04.01 |

| 윈도우10 레드스톤은 애니버서리 업데이트로 여름에 공개 (0) | 2016.04.01 |