인텔, 세계 최대 FPGA 칩 "Stratix 10 GX 10M" 발표

인텔은 14nm 기술에 기반한 놀라운 FPGA(Field Programmable Gate Array, FPGA) Stratix 10 GX 10M을 발표했다. 이는 세계에서 가장 큰 FPGA로 이전에 가장 큰 자일링스의 Virtex VU19P FPGA를 제압했다.

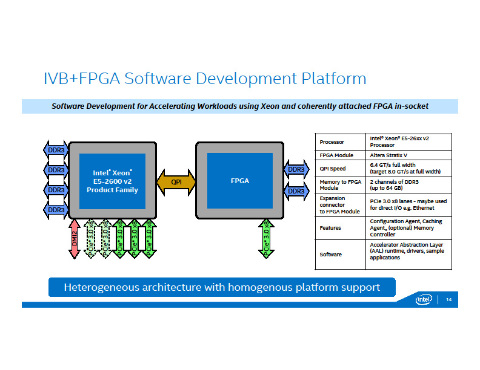

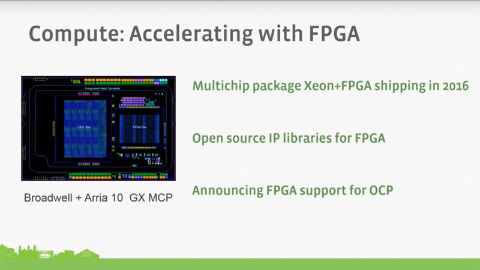

Stratix 10 GX 10M은 인텔 자체의 EMIB(Embedded Multi-die Interconnect Bridge)에 의해 연결된 2개의 대형 다이에 1,200만개 이상의 로직 셀이 내장되고 있다. 10M 모델은 EMIB로 연결되는 로직을 위한 2개의 로직 외 최대 4.5Tb/s의 총 대역폭을 갖는 48개의 트랜시버 포함 4개의 추가 다이를 패킹하고 있습니다. 모든 다이 사이의 대역폭은 EMIB의 25,920 연결로 판단 할 때 6.5Tb/s의 내부 다이 대역폭이 존재하므로 구성 요소가 데이터를 전송하기 위한 추가 속도에 부족하지 않을 것이며 또한 2,304개의 사용자 I/O핀이 있으므로 개발 목적으로 많은 포트가 포함된 창의적인 통합 솔루션을 사용할 수 있다.

출처 - https://www.techpowerup.com/260906/intel-unveils-worlds-largest-fpga

'글로벌 IT 뉴스' 카테고리의 다른 글

| 글로벌 반도체 기업 순위, 1위 인텔 및 TSMC의 위대한 성장 (0) | 2019.11.23 |

|---|---|

| AMD, 라이젠9 3950X, 3세대 스레드리퍼 3970X-3960X, 애슬론 3000G 발표 (0) | 2019.11.10 |

| AMD, Navi 14 기반 3개의 RX 5500 시리즈 및 2개의 RX 5300 SKU 준비 (0) | 2019.11.10 |

| AMD 실적발표, 인텔 CPU 공급부족으로 반사이익 (0) | 2019.11.03 |

| 2019년 3분기 전세계 PC 시장, 공급 문제에도 지속 성장 (0) | 2019.10.27 |