AMD 베가 GPU 아키텍처 개요 (HBM2, NCU, 캐시등)

6년만에 아키텍처가 쇄신 된 베가

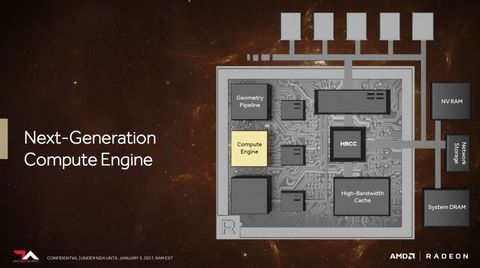

AMD의 차세대 GPU 아키텍처 "Vega(베가)"의 개요를 밝힌다. Vega는 AMD의 FinFET 세대의 플래그십 GPU다. 큰 특징은 GPU 마이크로 아키텍처를 쇄신하고 하이 퍼포먼스 하이엔드 GPU에 도입되는 것이다.

AMD는 서던 아일랜드(Southern Islands) 패밀리의 "Radeon HD 7900(Tahiti)"에서 "GCN(Graphics Core Next)"을 도입한 이후 GPU의 컴퓨트 유닛"CU(Compute Unit)"의 메이저 업그레이드는 진행하지 않았다. 베이스 아키텍처는 GCN 상태에서 상대적으로 마이너적인 확장을 가해 왔다. 그러나 이번 Vega는 마이크로 아키텍처를 일신해 CU 뿐 아니라 세이더의 제어 및 메모리 계층까지 모두 크게 변혁한다. AMD에게는 6년만의 GPU 아키텍처의 대변혁이다.

AMD는 FinFET 3D 트랜지스터 프로세스는 지난해(2016년) 퍼포먼스 GPU "Polaris"에 도입했다. 그러나 Polaris의 하이엔드 GPU는 공석이었으며 Vega 세대 "Vega 10"은 AMD에게 2년 만의 하이엔드 GPU다.

Vega 아키텍처는 그래픽스, 컴퓨트, 메모리 용량과 모든 면에서 퍼포먼스를 비약시킨다. 컴퓨트에서는 딥 러닝 대응과 FinFET 프로세스를 활용한 마이크로 아키텍처로의 전환. 딥 러닝용 데이터 밀도 도입과 GPU의 동작 클럭을 대폭 올린 아키텍처를 향했다.

그래픽에서는 지오 메트리 파이프 라인의 제어를 바꿨다. 새로운 Primitive Shader를 도입, 지오 메트리 처리량을 2배로 끌어올린다. 또 래스터라이저도 일신하고 설계 가능한 메소드를 도입했다. 이어 온 칩 메모리 계층에서는 백엔드도 L2로 캐시하도록 했다.

메모리 계층은 GPU에서 처음으로 비휘발성 메모리의 도입을 전제로 한 메모리 제어를 도입한다. 이는 가까운 장래에 약진할 것이라 기대되는 새로운 비휘발성 메모리 기술을 감안한 대응이다. 이 메모리 아키텍처는 AMD가 엑사플롭 슈퍼 컴퓨터의 메모리 모델로서 제안하고 있는 것과 같다. 또한 데이터 이동의 최적화를 함으로써 데이터의 쓸데없는 트래픽도 없앤다.

AMD의 Vega는 이처럼 그래픽 뿐만 아니라 컴퓨트와 비주얼 라이제이션까지 퍼포먼스를 강화한 새로운 아키텍처다.

마이크로 아키텍처가 바뀐 컴퓨트 유닛

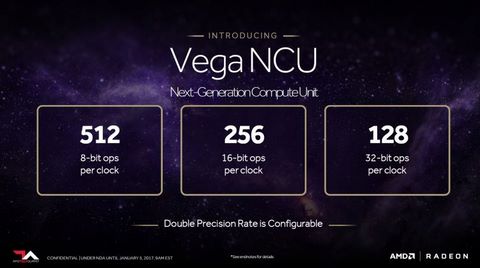

Vega의 CU(Compute Unit)는 "Next-Generation Compute Unit(NCU)"로 내부 마이크로 아키텍처가 일신된다. 아직 자세한 것은 밝혀지지 않았지만 핵심 차이는 밝혀졌다.

현재의 CU에서는 32-bit의 주산 16유닛으로 1개의 벡터 유닛을 구성하고 있다. 1개의 CU에는 4개의 벡터 유닛이 있어 합계 64의 32-bit 유닛을 갖춘다. 각 유닛이 평균 1클럭에 2작업 처리량이기 때문에 CU는 32-bit, 작업은 클럭당 128이 된다.

AMD GPU는 64스레드 배치인 Wavefront 단위로 처리 한다. 각 벡터 유닛은 16유닛으로 4사이클까지 Wavefront를 처리하는 구조다.

NCU에서는 새로운 저 데이터 밀도의 SIMD(Single Instruction, Multiple Data) 연산이 도입된다. 구체적으로는 2-way의 16-bit SIMD 연산과 4-way의 8-bit SIMD 연산이 가세한다. 이는 저 데이터 정밀도가 요구되는 머신 러닝 애플리케이션에 맞춘 확장이다.

AMD도 다른 GPU 제조 업체 같이 연산 유닛의 기본 데이터 밀도는 32-bit다. 그러나 딥 러닝에서는 성능을 올리기 위해 보다 정밀도가 낮은 16-bit와 8-bit가 사용되고 있다. AMD는 그러한 트렌드에 대응해 연산 유닛을 대폭 개편했다.

16-bit시 처리량은 32-bit시 2배, 8-bit시에는 처리량은 4배나 많다. AMD는 이미 Vega10 기반 GPU 컴퓨트용 "Radeon Instinct MI25"에서 하나의 카드로 16-bit 부동 소수점 연산에서 25TFLOPS를 달성하겠다고 밝혔다. NVIDIA의 Pascal(파스칼) 기준 "Tesla P100(GP100)"의 21TFLOPS(FP16)를 넘는다. 8-bit 운영은 더 배가되는 성능의 계산이다.

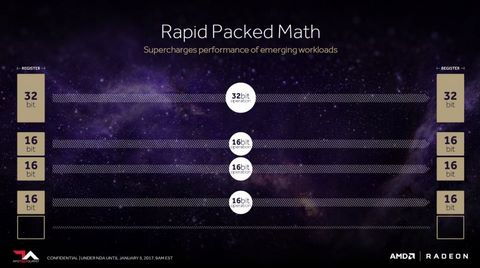

팩크드형 16-bit와 8-bit 연산 도입

AMD의 현재 아키텍처에서는 32-bit시 예측에 의해 조건 분기에 대응하고 있다. 단 벡터 유닛 속의 32-bit 각 레인은 같은 명령을 실행하는데 각각이 마스크 레지스터로 분기 패스만 실행되어 개별적으로 컨트롤 흐름이 제어된다. 그래서 32-bit시에는 외관상 독립된 스레드로 각 레인이 동작한다.

반면 이번에 도입된 16-bit와 8-bit의 연산은 팩크드(packed)형, 즉 SIMD다. 32-bit의 1레인에서 16-bit시에는 2데이터가, 8-bit시에는 4데이터가 포장되고 같은 명령을 실행한다. 16-bit와 8-bit는 각각 다른 분기 패스를 실행할 수 없다. 그러나 딥 러닝 용도의 경우 팩크드로 대응할 수 있기 때문에 연산 성능이 향상하는 만큼 성능이 올라간다.

GPU에 대한 팩크드 포맷의 저 데이터 밀도 연산의 도입은 딥 러닝 시대에 들어 트렌드다. NVIDIA도 대응을 추진하고 있고 Imagination Technologies의 PowerVR 등도 대응하고 있다.

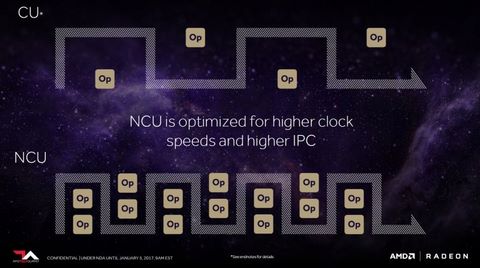

Vega NCU의 또 한가지 중요한 특징은 고클럭화다. AMD는 클럭을 높이기 위해 파이프 라인을 변경했다고 본다. 파이프 라인 단수가 2배가 되면 원리적으로는 GPU 코어의 동작 주파수를 두배 가까이 올릴 수 있게 된다. 이것도 FinFET 프로세스 시대에 들어선 GPU 코어의 트렌드가 되고 있다.

FinFET에서는 리크 전류(Leakage)가 크게 떨어지면서 동작 주파수의 액티브 전력도 낮출 수 있다. 그래서 파이프 라인의 세분화에 의한 고클럭화를 행하는 것이 가능하게 된다. 전력 하락분을 고클럭화로 돌리는 것이다.

파이프 라인 단수를 늘리면 파이프 라인 중인 데이터를 유지하는 래치 회로가 늘어난다. 래치는 논리 회로 중의 큰 전력 소비원이기 때문에 누설 전류(Leakage)가 많은 프로세스에서는 파이프 라인 단수를 늘리기 어려웠다. 그러나 Vega는 저 누설 전류(Leakage)의 14nm FinFET 프로세스로 제조되기 때문에 파이프 라인 단수를 늘릴 수 있다.

폭발하는 데이터양에 대응하기 위한 메모리 계층

GPU는 현재 취급하는 데이터 양의 폭발적인 증대에 직면하고 있다. 게임 설치 크기는 격증했고 영화 제작 등 전문 그래픽 데이터 양도 급격히 대형화되고 빅 데이터 분석과 머신 러닝에 의해 컴퓨트의 데이터량은 천문학적인 숫자로 불어나고 있다.

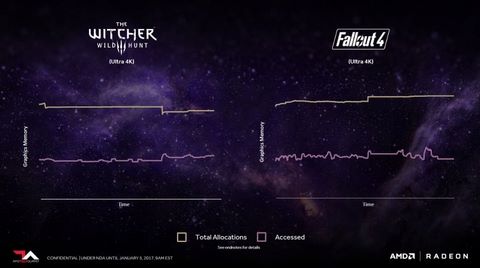

문제는 GPU의 메모리 용량이 그러한 데이터량의 증대 및 GPU 연산 성능의 증대에 걸맞게 늘지 않는다는 것이다. 거기서 Vega는 새로운 메모리 계층의 어프로치를 도입한다. GPU 메모리를 광대역 캐시로 취급하고 GPU 외부의 메모리를 빠짐없이 다룰 수 있도록 한다.

구체적으로는 Vega는 스택 DRAM "HBM2"를 GPU 메모리로 도입한다. Vega10에서는 2스택이다. 그러나 GPU 패키지 인터포즈 위에 올라간 HBM2 만 아니라 오프 패키지의 메모리도 GPU가 다루도록 한다. HBM2는 마치 캐시처럼 다루는, 하드웨어 제어에서 태그 RAM을 갖춘 캐시가 아니라 메모리 제어로서 워킹 메모리로 다루는 이미지다.

비휘발성 메모리(NVRAM)를 포함한 메모리를 GPU가 직접 챙기면서 혹은 직접 다루고 있는 것 같이 할 수 있는 구조를 준비한다. GPU의 DRAM 용량을 그냥 늘리는 것이 아니라 어드레싱할 수 있는 메모리를 다양화하는 것으로 대용량화되는 데이터에 대응한다. 그래서 Vega10에서는 512TB까지 가상 주소 공간을 지원한다. 그리고 계층화된 메모리 간에 효율적으로 메모리를 얼로케이트함으로써 고성능으로 저전력 메모리를 실현한다.

새로운 세이더 스테이지와 래스터 라이저, 캐시 계층의 개량

지오 메트리 파이프 라인은 버텍스 세이더(Vertex Shader)와 함께 지오 메트리 세이더(Geometry Shader)을 거친다. Vega는 새로운 지오 메트리 경로로 Primitive Shader를 도입한다. Primitive 단위로 취급함으로써 피크 처리량을 높인다. 또 렌더링 파이프 라인 전체 워크 로드의 제어도 지능화된다.

AMD 아키텍쳐는 렌더링 백엔드와 텍스처 액세스는 일관되지 않는다. 그래서 렌더링 투 텍스처에 텍스처를 쓰는 경우에는 GPU 내부 캐시 계층을 쓰지 못했다. Vega는 렌더링 백엔드도 L2 캐시로 캐싱 되며 L2에서 캐시 하는 텍스쳐와 일관되며 지오 메트리에서 픽셀에 대한 래스터 라이즈도 스마트화됐다. 이는 VR(Virtual Reality) 같은 두가지 관점의 어플리케이션으로 효과를 발휘할 것으로 보인다.

출처 - http://pc.watch.impress.co.jp/docs/column/kaigai/1037849.html

'글로벌 IT 뉴스' 카테고리의 다른 글

| 레이저, 3개의 4K 모니터를 탑재한 프로젝트 벨러리 발표 (0) | 2017.01.06 |

|---|---|

| 인텔 10나노 캐논레이크 시연, 무어의 법칙은 계속된다 (0) | 2017.01.06 |

| 웨스턴 디지털, NVMe 대응 WD Black SSD 발표 (0) | 2017.01.05 |

| 펜 입력/3D 스캐너 탑재 23.8형 일체형 HP 스프라우트 프로 발표 (0) | 2017.01.05 |

| 알파고, 커제등 세계 최정상 바둑기사를 가볍게 격파 (0) | 2017.01.05 |