인텔이 외장형 GPU 프로토 타입 발표 (ISSCC)

인텔은 AMD에서 Radeon GPU 부문의 수장이였던 Raja Koduri(라자 코두리)를 영입해 Core and Visual Computing Group의 Chief Architect & Senior Vice President로 임명했다. 이 극적인 이적으로 인텔이 디스크 리트 GPU(외장형 GPU)에 진출하는 것 아니냐는 관측이 일부에서 흐르고 있었다. 그런 시점에서 인텔은 미국 샌프란시스코에서 열린 반도체 국제 회의 ISSCC(IEEE International Solid-State Circuits Conference)에서 디스크 리트 GPU의 개발 칩을 발표했다.

이번 개발 칩은 제품으로서 시장에 내놓는 수준은 아니다. 어디까지나 기술 검증을 위한 GPU 칩으로 기존의 인텔 내장 GPU 아키텍처를 바탕으로 IVR(Integrated Voltage Regulator:통합 전압 조정기)를 사용한 전력과 퍼포먼스 제어 기술을 검증한 것이다.

인텔은 과거에도 이런 전력 절약 기능 검증을 위한 GPU 칩을 개발했으며 2014년에도 ISSCC에서 22nnm의 프로토 타입 칩을 발표하고 있다.("5.7 A Graphics Execution Core in 22nm CMOS Featuring Adaptive Clocking, Selective Boosting and State-Retentive Sleep"S. B. Nasir, et al., ISSCC 2014) 하지만 이 프로토 타입 칩은 GPU로서 풀 기능을 갖추고 있고 확장하면 제품으로 만드는 것도 불가능하지 않다.

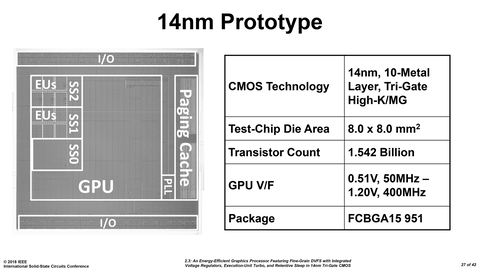

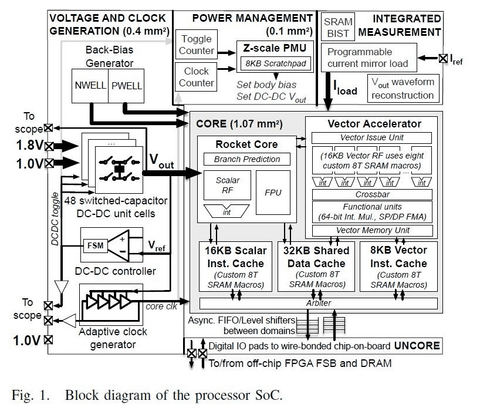

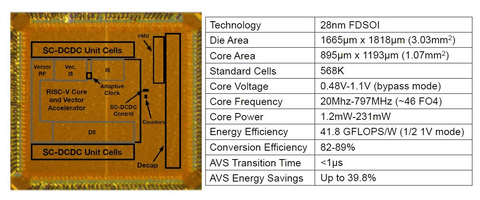

이번에 개발한 GPU 아키텍처는 최신 Intel Graphics Gen9 세대로 인텔의 표준적인 GPU 코어지만 실장은 LP, 즉 Atom계 CPU 아키텍처 SoC에 혼재된 저전력의 GPU 코어로 구현했으며 스탠더드 셀 라이브러리 등이 PC용과 다른 것으로 보인다. 프로세스는 인텔의 14nm로 10메탈(배선)층, 다이 사이즈는 8×8mm, 1.5B 트랜지스터, 동작 주파수와 전압은 50MHz/0.51V에서 400MHz/1.2V. 트랜지스터 수가 많은 것은 캐시 SRAM을 대량 탑재하고 있기 때문이다.

인텔의 내장 GPU 코어를 기반으로 새로운 설계 도입

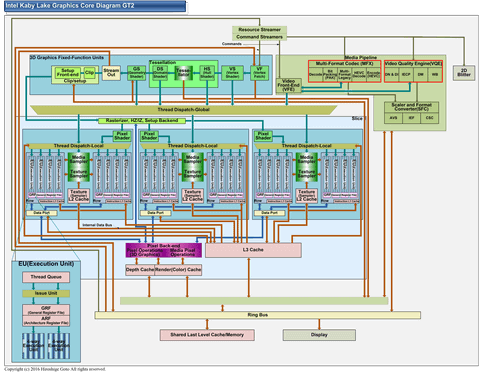

인텔의 GPU 코어는 "EU(Execution Unit)"로 불리는 벡터 코어로 구성된다. 1개의 EU는 2개 4-way 벡터 유닛을 탑재한다. FP32(32-bit 부동 소수점 연산) 유닛이 4-way 128-bit 벡터 유닛이다. EU에는 2개 벡터 유닛과 7 멀티 스레드 범용 레지스터(GRF), 브랜치 유닛이 포함된다.

프로토 타입 칩에는 EU가 6개 바인드 된 "Sub-Slice(SS:서브 슬라이스)"를 구성하고 있다. 서브 슬라이스에는 EU 뿐 아니라 텍스쳐 유닛이나 L1/L2 캐시, 스레드 디스패치, 데이터 포트 등이 부속된다.

이번 칩에서 3개의 서브 슬라이스로 1개의 "Slice(슬라이스)"를 구성하고 있는 것으로 보인다. 다이 사진에는 SS0에서 SS2까지 3개의 EU가 보인다. 3개의 EU 서브 슬라이스 가운데 이번 새로운 전력 제어 장치가 장착된 것은 2개. SS1과 SS2가 새 설계의 EU다.

SS0은 비교용으로 종래의 설계. 3개의 SS로 구성되는 슬라이스는 풀 기능의 GPU 코어가 되고 있어 그래픽 고정 함수(FF:Fixed Function)와 명령 스트리머, L3 캐시 등을 내포한다.

테스트 칩은 1슬라이스 구성에서 모두 3개의 서브 슬라이스, 18개의 EU를 탑재한다. 벡터 유닛 내 FP32의 주산 유닛은 합계 144 유닛이다. PC용 인텔 그래픽의 로우 엔드 GT1은 표준 장착으로 96 FP32.

테스트 칩은 주파수가 낮은 LP 구현에서 144 유닛으로 로우 엔드의 PC용 그래픽 수준의 성능과 같다. 또 통상의 GPU 코어에는 동영상 코덱 등을 포함한 멀티미디어 코어가 포함되지만 이번 프로토 타입 칩에 포함되어 있는지는 명기되지 않았다.

ISSCC에서 발표된 GPU 칩에는 GPU 코어만 아니라 제어나 I/O 주변을 포함한 System Agent(SA:시스템 에이전트)가 탑재되어 있다. 메모리 인터페이스는 호스트 측 그 때문인지 SA에 4MB와 풍성한 페이징 캐시도 탑재되고 있다. 호스트 PC는 FPGA 브리지를 경유하여 연결된다. 구성을 보면 실증 실험용 프로토 타입이다.

IVR을 활용한 세밀한 전압/주파수 제어

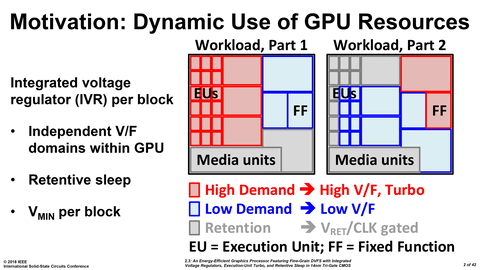

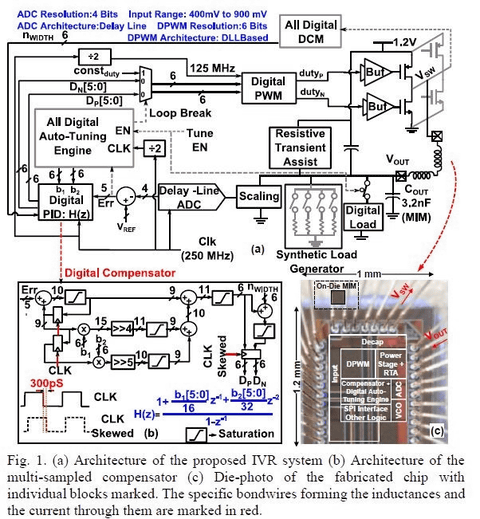

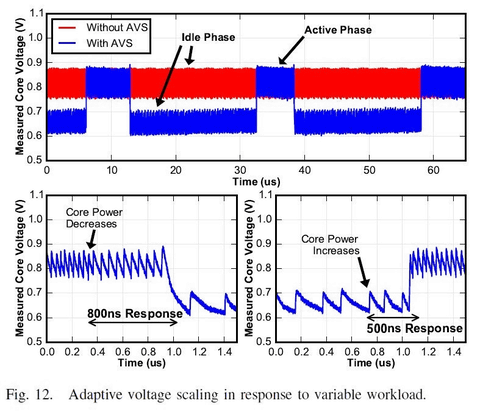

인텔의 이번 테스트 칩의 최대 특징은 IVR을 사용한 V/F(Voltage/Frequency:전압/주파수) 제어나 파워게이팅을 하고 있는 점이다. 전통적으로 GPU는 CPU와 비교해서 이런 V/F 제어 및 전력 절약 기능이 약하다. 이는 전통적인 그래픽 워크 로드는 고 부하가 일정 기간 이어지거나 아니면 부하가 극히 가볍거나로 치중되기 때문이다. GPU 벤더도 GPU의 전력 제어는 그리 주력하지 않았다.

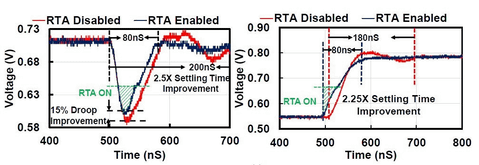

그러나 인텔은 GPU 코어에 세밀한 전력 제어를 도입하는 것이므로 조건에 따라서는 성능 효율을 향상시킬 수 있음을 실증했다. 전력 절약 제어에 뛰어난 Intel CPU 코어의 노하우를 활용하여 CPU에서 보다 더 나은 전력 제어를 GPU 코어에 적용함으로써 효과가 발휘되는 것을 나타냈다. GPU에 입도가 작은 각종 태스크가 달리게 되면 이러한 전력 제어가 보다 효과를 거둘 것이다.

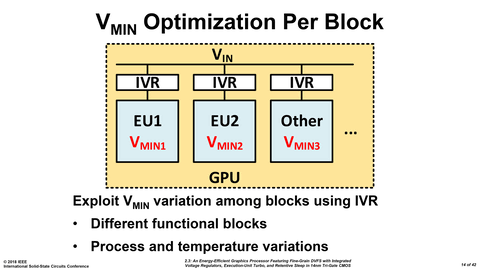

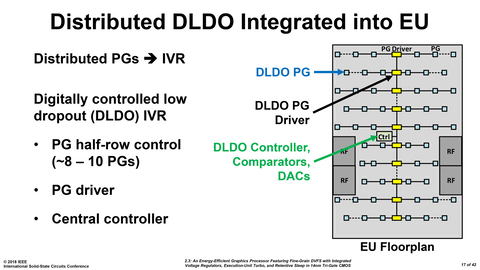

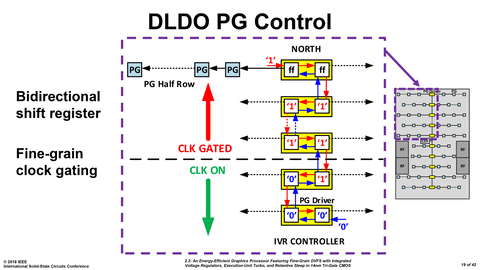

기본적인 아이디어는 GPU를 세립 블록 단위로 동작 주파수와 전압 제어, 필요한 블록이 최적의 주파수와 전력에서 동작하도록 한다. 그 때 온 다이(On-Die)에 통합한 IVR(통합 전압 조정기)로 고속의 전압 변환을 가능하게 한다. 우상 상태의 블록은 레지스터 등의 SRAM 데이터를 보유할 수 있는 한계의 모관 전압까지 떨어뜨리고 리크 전류를 억제한다. 파워 게이트(PG)는 GPU에 분산된 PG 드라이버를 통해 신뢰성이 높은 웨이크 업 장치로 제어한다.

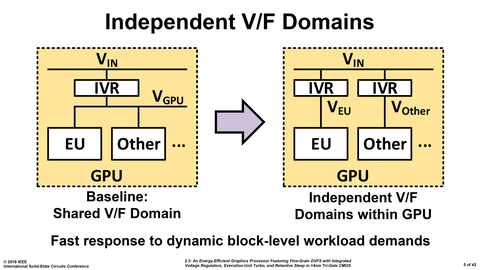

IVR 도입으로 유닛별 전압 변환이 가능하게

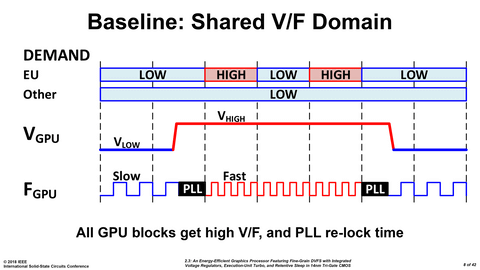

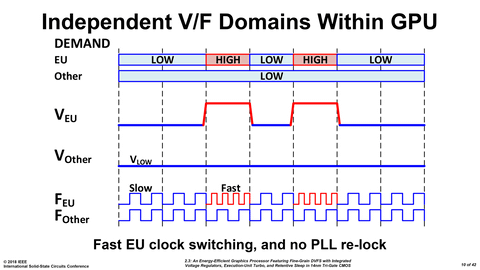

기존의 인텔 설계에서는 GPU 전체에 대해 IVR에서 단일 전압(Vgpu)으로 전력이 공급되고 있었다. 아래 슬라이드 왼쪽의 그림 같은 형태다. 반면 이번 설계에서는 GPU 안의 연산 유닛인 EU와 다른 유닛에는 개별 전압으로 전력이 공급되어 슬라이드 오른쪽 그림과 같이 된다.각각 독립된 IVR이 할당된다.

기존의 경우는 컴퓨트 태스크의 경우 EU의 부담이 커졌으며 그 결과 GPU 전체의 전압이 높게 전이해 클럭은 PLL의 리-록에 따라 고 클럭으로 전환된다. 그때 EU 이외의 유닛은 부하가 낮아도 EU와 해당 전압, 해당 클럭에 밀려 GPU 코어 전체의 소비 전력이 상승한다.

반면 EU와 다른 유닛을 개별적으로 주파수와 전압을 제어할 경우 더 유연하게 된다. EU의 전압만 부하에 맞추어 오르면서 EU의 작동 주파수는 정기 주파수의 2배로 바뀐다. 개별적으로 반응성이 높은 IVR을 장착함으로써 전압의 상승을 단시간에 가능하게 한다.

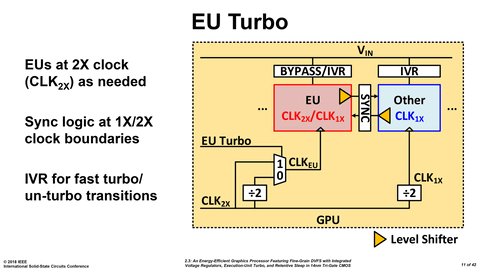

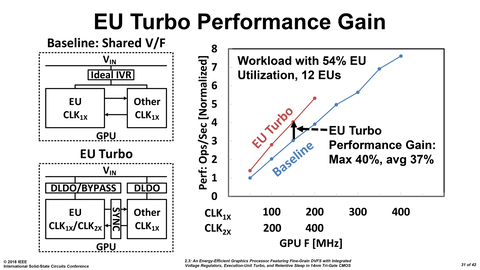

또 주파수는 두배의 속도로 대체함으로써 PLL의 리-록이 불필요하다. 인텔은 이를 "EU Turbo(EU 터보)"라고 부른다. 기준 클럭을 2x 에서 공급하고 보통시 그 클럭을 절반에 공급, 터보시 본래의 2x 클럭으로 전환한다. 결과적으로 부하에 따라 신속히 응답하는 전압/주파수 변환이 가능하다.

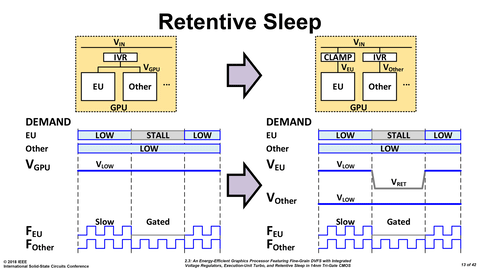

반대로 EU가 단시간의 스톨에 들어갔을 때는 EU 부의 전압을 리텐션 전압으로 떨어뜨리고 클럭 공급을 끊어 슬리프 상태로 만든다. 종래에는 클럭 게이트시 전압을 지울 수 없었지만 ISSCC에서는 EU의 IVR이 독립되기 때문에 EU의 전압을 SRAM이 보유할 수 있는 하한의 전압으로 떨어뜨려 전력을 감소시킨다.

또 EU에 각각 개별적으로 IVR을 설치함으로써 동작할 수 있는 최저 전압 Vmin의 편차를 조정할 수도 있다. 프로세스 자체의 차이만 아니라 온도의 편차도 있지만 IVR에서 동적으로 각 유닛의 Vmin을 조정할 수 있다. 그래서 Vmin을 유닛마다 최저 전압으로 할 수 있다.

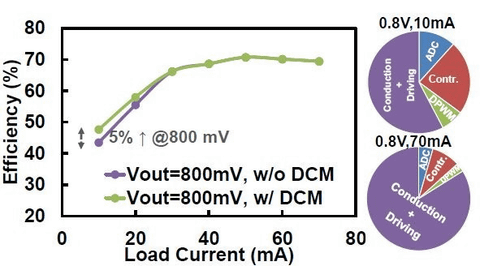

2종류의 IVR을 GPU에 통합

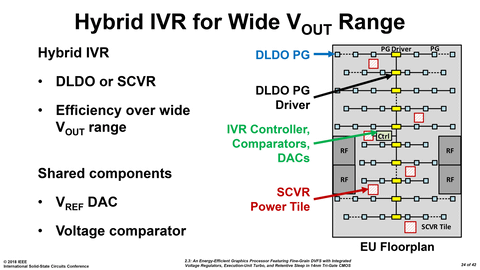

이번 개발 칩의 IVR 특징은 2가지의 다른 VR을 통합한 하이브리드 설계를 취한데 있다. 인텔이 이전부터 도입하고 있던 "Switched Capacitor VR(SCVR)" 뿐 아니라 "Digitally Controlled Low Dropout(DLDO)"을 병용하고 있다. 2종류의 IVR에 의해 폭넓은 전압 범위로 높은 전압 변환 효율을 실현한다.

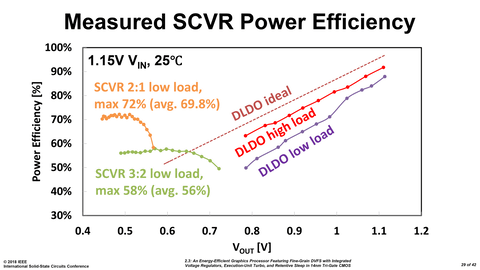

입출력 간 전위차가 작은 경우에 유효한 DLDO를 통상의 동작시에 사용. 1.15V의 입력 전압(Vin)에 0.785V~1.11V 정도의 출력 전압(Vout). 세립 제어는 DLDO를 바탕으로 한다. MIM 캐패시터를 내장하는 SCVR은 출력 전압이 0.3V~0.7V로 낮은 경우에 사용한다. 입력에 대한 출력의 전위가 3:2,2:1,3:1의 비율.

EU 내부에는 SCVR이 6타일 배치되고 있다. 그리고 DLDO는 EU의 중앙에 척수처럼 컨트롤러가 배치되고 DLDO로 제어되는 파워 게이트(PG)가 EU 전체에 체스판 패턴으로 배치되고 있다. 1400 이상의 PG 배치라고 한다.

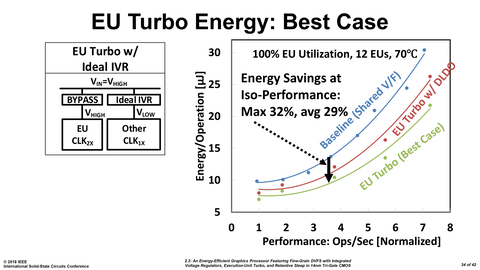

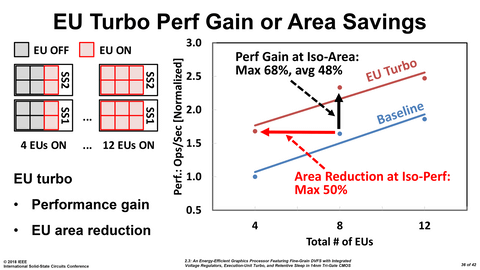

신설계의 12 EU에 대해서 EU의 워크 로드 점유율이 54%인 경우 EU 터보의 성능 향상은 최대 40%, 평균 37%가 된다. 100%의 EU 점유율시 EU 터보에 의해 베이스 라인보다 최대 32%, 평균 29%의 전력 저감이 가능하다. 또 EU 터보를 사용하고 EU의 동작 주파수를 향상시키면서 일부 EU을 파워 게이트함으로써 전력 저감 및 성능 향상을 실현한다.

이번에 인텔이 발표한 프로토 타입 GPU는 제품화로 가려는 레벨은 아니다. 그러나 인텔의 프로세서에 대한 전력 제어 설계의 방향성이 보이는 점은 흥미롭다.

인텔은 IVR 실장에 계속하고 진지하게 임하고 있어 Haswell 세대보다 앞선 설계를 시도하고 있다. 그것도 CPU 뿐 아니라 GPU 코어에도 적용하고 있다. 인텔의 전력 제어는 실은 인텔의 보이지 않는 강점이며 AMD가 쫓아오고 있는 부분이기도 하다. 향후 진화가 주목된다.

출처 - https://pc.watch.impress.co.jp/docs/column/kaigai/1107078.html

'글로벌 IT 뉴스' 카테고리의 다른 글

| 차기 아이폰 시리즈의 6.5인치 모델 디스플레이 사진 유출 (0) | 2018.02.25 |

|---|---|

| 퀄컴, 브로드컴의 1200억달러 인수 제안도 거부 (0) | 2018.02.19 |

| 애플, 본사 주소를 Infinite Loop에서 새로운 Apple Park로 변경 (0) | 2018.02.18 |

| 블록체인, 게임산업에 다양한 변화를 불러올 전망 (0) | 2018.02.18 |

| 블록체인, 탈 집중화된 콘텐츠 방식으로 Cable TV와 Netflix 위협 (0) | 2018.02.18 |