TSMC의 최첨단 반도체 패키지 기술, InFO / CoWoS

반도체 파운드리 최대 기업인 TSMC는 웨이퍼 수준의 최첨단 패키지 기술을 제공하는 것으로 최근 주목을 받고 있다.

특히 스마트폰 제조 업체인 Apple이 iPhone7 용 애플리케이션 프로세서 A10의 제조 위탁 업체에 TSMC에 올인한 근거가 이 회사가 제공하는 패키지 기술 "InFO(Integrated Fan-Out WLP)" 때문인 것 같다는 이야기로 TSMC의 이름은 반도체 업계 뿐만 아니라 하드웨어 기술을 좋아하는 스마트폰 사용자에게도 알려지게 됐다.

TSMC는 스마트폰과 웨어러블 단말기 등의 기간 부품을 위한 새로운 패키지 기술을 InFO기술을 기반으로 개발 중이다. 그 일부를 국제 학회 "VLSI 기술 심포지엄"에서 공표했다.(강연 번호 JFS2-3)

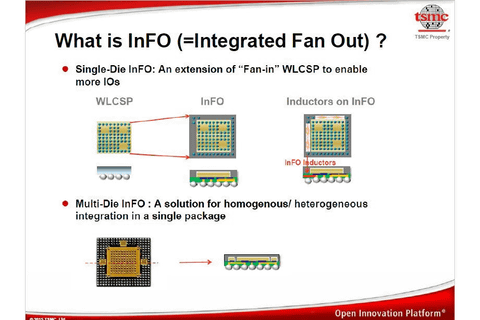

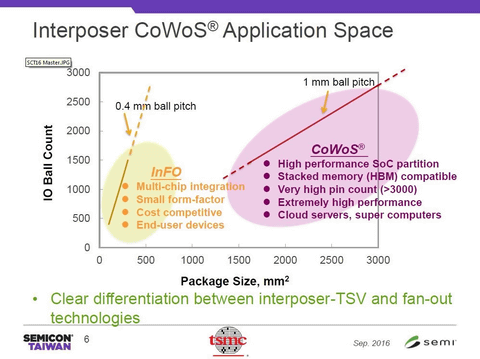

초박막 패키지 "InFO"는 두께가 불과 0.5mm로 기판이 없는데 따른 재료비 절감, 웨이퍼 수준의 일괄 생산에 따른 제조 비용 절감을 양립시키는 뛰어난 패키지다. TSMC는 차세대 패키지로 "InFO"와 "CoWoS(Chip on Wafer on Substrate)"의 2개 기술을 개발하고, 양산에 들어갔다.

"InFO"는 모바일 단말기 전용, "CoWoS"은 고성능 컴퓨팅용이라는 차이가 있다.

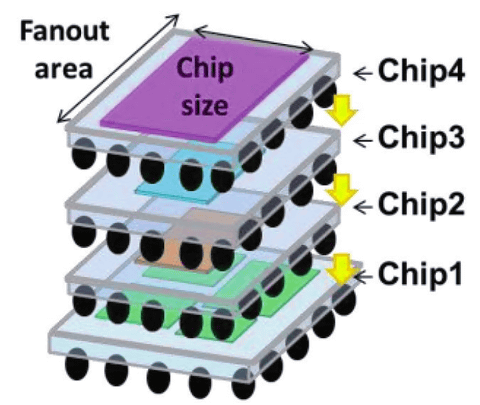

초박형 패키지 "InFO"를 적층 하는 스택 모듈

"VLSI 기술 심포지엄"에서 TSMC는 InFO를 위아래로 적층 하는 스택형 InFO 패키지 기술이라고 밝혔다. 적층 수로는 당초 4층 정도를 상정한다. 이는 타당한 층수이며 2층은 현행 InFO 기술로 대응할 수 있고, 8층이 되면 제조 기술의 난이도가 높아진다.

스택형 InFO 패키지 기술의 기반이 되고 있는 것은 TSMC가 "InFO-PoP(Package-on-Package)" 이라 부르며 InFO 패키지 위에 반도체 패키지를 탑재하는 패키지 기술이다.

InFO-PoP 기술의 특징은 "TIV(Through InFO Via)" 라고 불리는 몰드 수지를 관통하는 전극(구리 전극)에 의해 상하 실리콘 다이를 연결하는 것이다. InFO-PoP 기술은 InFO 패키지의 실리콘 다이에 애플리케이션 프로세서, InFO 패키지 위에 올리는 반도체 디바이스는 LPDDR 계열 DRAM(패키지품)을 상정하고 있었는데 이를 확장한 것이 "InFO 패키지 온 InFO 패키지" 라는 이번 개발 기술이라 하겠다.

VLSI 기술 심포지엄에서 TSMC는 4개의 InFO 패키지를 적층한 모듈을 개발하고 단면 구조를 X선에서 관찰한 화상이나 방열 특성을 TSV(Trough Silicon Via)적층 모듈과 비교한 결과 등을 보였다. TSV 기술에 의해 4장의 실리콘 다이를 적층 했을 때보다 양호한 방열 특성을 얻었다고 한다.

TSV(실리콘 관통 전극)의 이상과 현실

최근까지 실리콘 다이를 수직으로 적층하는 패키지 기술로는 TSV(Trough Silicon Via, 실리콘 관통 전극) 기술이 가장 유력시되고 있었다. TSV 기술은 실리콘 다이에 구리(Cu) 관통 전극을 형성하면서 적층한 실리콘 다이들을 접속한다. 적층한 실리콘 다이들을 최단 거리로 접속하는 기술로 고속·고주파·저전력이라는 3가지 갖춰진 다음 패키지 기술로서 큰 기대를 걸고 있었다.

그러나 현재는 일부 고성능 컴퓨팅 분야를 제외하고 TSV 기술은 크게 보급될 수 없다는 견해가 강해지고 있다. 확실히 GPU와 메모리가 일체화 된 모듈에서는 DRAM 다이를 적층하는 HBM(High Bandwidth Memory)에 TSV 기술이 채용되고 있다. 그러나 하이엔드 GPU용 HBM을 제외하면 TSV 기술의 상용화 사례는 거의 없다고 말해도 좋은 상태다.

TSV 기술이 보급되지 않는 가장 단순한 이유는 제조 비용이 높은 것이다. 우선 처음에 실리콘에 관통 구멍(비아)을 형성하고 구리(Cu)를 박기 위한 비용이 꾀 든다. 다음에 구리의 관통 전극과 실리콘의 사이에 응력이 발생하고 트랜지스터의 특성을 바꾼다는 문제가 있다. 관통 전극 부근에는 응력을 완화하기 위한 데드 스페이스를 마련해야 한다.(트랜지스터를 배치할 수 없다) 이 때문에 실리콘 다이 면적이 늘면서 제조 비용이 더 상승한다.

또 적층 공정은 접속용 미세한 밴프(마이크로 범프)를 고정밀로 실리콘 다이에 탑재하는 동시에 실리콘 다이들을 정확하게 위치에 맞추어 올려야 한다. 이것도 나름의 비용이 증가된다.

문제는 제조 비용만이 아니다. TSV 기술에서 실리콘 다이를 적층 하는 경우에는 상하의 실리콘 다이간에 크기에 제한이 있다.

간단히 말하면 아래의 실리콘 다이의 치수에 대한 위의 실리콘 다이는 같은 치수 또는 작은 치수이어야 한다. 위쪽에서 본 경우 위의 실리콘 다이가 아래 실리콘 다이에서 벗어날 수 없다. 이렇게 되면 TSV 기술의 응용 분야는 같은 종류의 실리콘 다이를 거듭한 메모리 응용에 한정되기 쉽다.

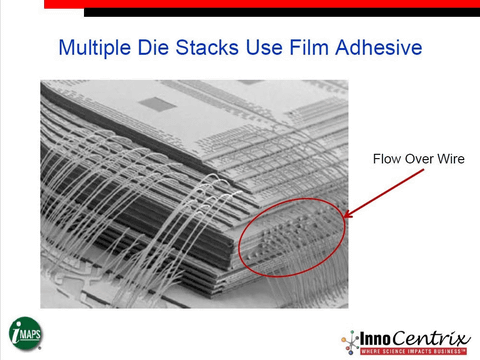

그런데 단순히 같은 실리콘 다이를 거듭한다면 값싼 와이어 본딩 기술로 충분히 가능한 것이다. 예를 들면 HBM2는 최고 8장의 DRAM 층을 거듭하고 있다. 와이어 본딩 기술에서도 8장 적층은 간단하지는 않지만 충분한 상용 실적을 갖는다. 그리고 제조 비용은 TSV 기술보다 훨씬 낮다. 8장 적층은 커녕 16장 적층도 와이어 본딩 기술로 상용 실적이 있다.

예를 들면 NAND 플래시 메모리 모듈인 eMMC(embedded Multi Media Card)는 컨트롤러의 실리콘 다이 1장 위에 16장의 NAND 플래시 실리콘 다이를 와이어 본딩 기술로 적층 하는 제품이 있다.

그럼 왜 HBM 모듈에서 TSV 기술을 도입했을까? HBM 모듈에서는 1000핀을 넘는 극히 수많은 입출력 단자를 처리해야 하기 때문이다.

InFO 기술로 실리콘 다이를 적층한 큰 장점

스택형 InFO 패키지 기술은 1000핀을 넘는 입출력 단자를 처리할 수 있다. 그리고 TSV 기술을 사용하지 않기 때문에 제조 비용이 낮다. 또 다른 치수의 실리콘 다이를 수직으로 적층할 수 있는 여러가지 장점이 있다.

특히 다른 치수의 실리콘 다이를 수직으로 적층 할 수 있는 장점은 주목해야 할 것이다. 로직, 메모리, 이미지 센서, 아날로그와 같은 제조 기술과 다이 면적이 전혀 다른 실리콘을 적층할때 얇고 작은 패키지로 마무리되는 기술은 별로 없다.

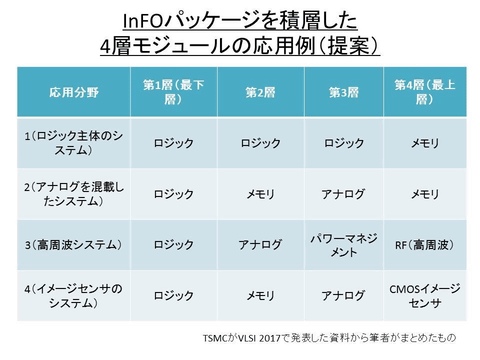

TSMC는 VLSI 기술 심포지엄 강연에서 다른 종류의 실리콘 다이를 적층 하는 것으로 여러 응용 분야를 위한 시스템을 구축할 수 있음을 보여줬다. 메모리를 혼재하는 시스템, 아날로그를 혼재하는 시스템, 고주파 트랜시버와 카메라 모듈 등이 있었다.

궁금한 것은 적층 수다. 시스템 응용을 생각하면 4층은 적은 것 같다. 이 기술이 16층이라는 수 많은 수량에 대응할 수 있을지는 미지수다.

그래도 제조 비용이 상당히 낮은 것이나 소형 평판인 것, 그리고 실리콘을 가리지 않는 것은 매력적이며 향후 전개가 기다려지는 기술이다.

출처 - http://pc.watch.impress.co.jp/docs/column/semicon/1065205.html

'글로벌 IT 뉴스' 카테고리의 다른 글

| 아이픽스잇, 신형 서피스 프로 분해 사진 공개 (0) | 2017.06.17 |

|---|---|

| 고급 사운드카드 등장, 사운드 블라스터X AE-5 (0) | 2017.06.17 |

| 글로벌 파운드리, 7나노 핀펫(7LP) 관련 내용 발표 (0) | 2017.06.17 |

| 메쉬 인터커넥트, 인텔의 새로운 상호 연결 기술 (0) | 2017.06.17 |

| 델, 37.5형 울트라샤프 38 커브드 모니터(U3818DW) 발표 (0) | 2017.06.14 |