메모리 벤더가 차세대 DRAM에 대해 공개 시작

DRAM 벤더나 칩 벤더가 드디어 차세대 메모리 군에 대해 본격적으로 공개했다. 미국 샌프란시스코에서 8월 16 ~ 18일에 개최된 인텔의 개발자 컨퍼런스 "Intel Developer Forum(IDF)16" 에서 차세대 메모리 규격이 기술 세션에서 등장했다. "DDR5"나 "LPDDR5", 광대역 메모리 "HBM3" 등의 사양 일부나 투입 스케줄 등이 밝혀졌다. 또 미국 쿠퍼티노에서 개최되고 있는 칩 컨퍼런스 "Hot Chips 28"에서도 튜토리얼 세션에서 "GDDR6"와 DDR5, LPDDR5, "Low Cost HBM" 등 차세대 DRAM에 대한 설명이 있었다.

DRAM은 프로세스 기술 상의 제약이 강해고 미세화와 함께 제조 비용이 높아지고 있다. 또 메모리/스토리지 계층 자체가 변혁기에 접어들며 DRAM과 SSD 사이에 들어가는 비휘발성 메모리로 DRAM 용량에 대한 요구는 부분적으로 가라앉고 있다. 그러나 저 레이턴시로 광대역 DRAM을 요구하는 트렌드 자체는 건재하여 새로운 DRAM 인터페이스가 필요하다.

DRAM시장 자체는 데스크탑&노트 PC의 비율이 감소되고 모바일과 서버의 비율이 상승했다. 그래서 DRAM에 대한 요구도 바뀌고 있다. 칩 수가 제한되는 모바일과 대용량이 필요한 서버가 중심이 되면서 전력 절약과 패키지의 대용량 화가 중요하다.

앞으로 수 년간 PC와 서버의 메모리 모듈용으로 DDR5, 스마트폰 등 모바일 기기 등에 LPDDR5, 그래픽 등에 GDDR6, 광대역 메모리에는 HBM3와 Low Cost HBM, 동시에 이미 양산에 들어가고 있는 "GDDR5X"와 "LPDDR4X", "HMC gen2" 등 다양한 DRAM 기술이 투입된다.

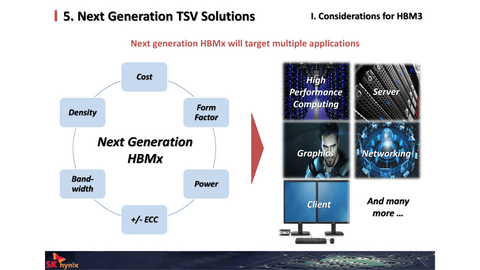

그것과 동시에 메모리 대역도 확대되어 간다. 스마트폰의 메모리 대역은 50GB/s 이상, 하이엔드 GPU와 고성능 컴퓨팅(HPC)은 2TB/s이상, 미들 레인지 GPU는 500GB/s 이상, GPU가 내장된 클라이언트 CPU는 300GB/s 정도로 확대될 것으로 보인다. 간단히 말하면 현재보다 2~3배의 메모리 대역으로 확대되고 소비 전력은 일정하게 통제한다. 이것이 현재의 메모리 비전이다.

규격화는 진행되고 있지만 침투는 늦은 DDR5

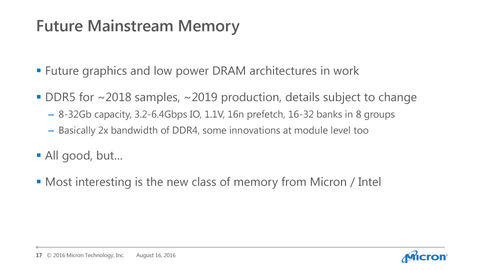

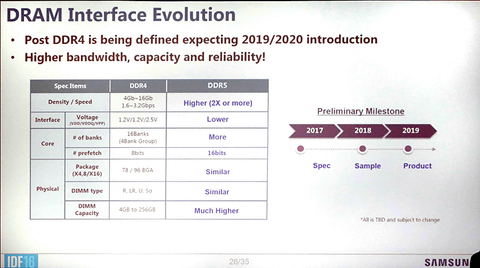

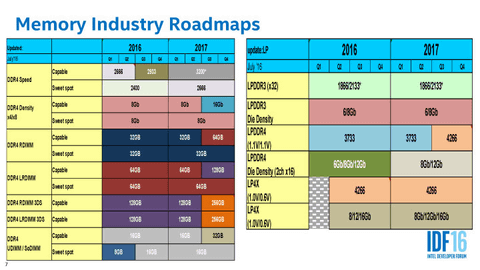

메인 스트림 메모리 모듈용 DDR 시스템 메모리는 차세대 DDR5가 JEDEC(반도체 표준화 단체)에서 규격 책정이 진행되고 있다. DDR5는 최대 6.4Gbps의 전송 속도와 DDR4의 2배의 속도가 될 전망이다. 듀얼 채널 메모리라면 100GB/s 정도의 메모리 대역이다. 칩 용량은 32G-bit까지의 대용량을 지원(DDR4는 16G-bit까지), 메모리 뱅크 수는 최대 32뱅크다.(DDR4는 16뱅크까지)

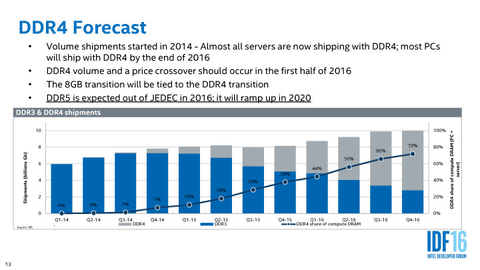

다만 DDR5의 시장 침투는 신세대 DRAM 중에서는 상당히 슬로우 페이스가 될 것 같다. 인텔의 Geof Findley(Director, Memory Ecosystem Manager, DCG Platform Memory Operations, Intel)는 IDF에서 규격 자체는 올해(2016년)에 결정되겠지만 본격적으로는 2020년경에 될 것이라 밝혔다. Micron도 샘플은 2018년 양산은 2019년 예정이지만 2020년으로 늦어질 것이라고 Hot Chips에서 설명했다. IDF에서 삼성의 밝혀진 스케줄도 2017년까지 규격 릴리즈, 2018년에 샘플, 2019년 양산이다. 그러나 DDR5의 운명은 최대 사용자인 인텔의 로드맵에 의해 좌우된다.

DDR5는 전압도 1.1V로 떨어진다(DDR4는 모두 1.2V). 전력 효율은 DDR4보다 높아질 전망이다. 선반입은 DDR4의 8-bit에 비해 DDR5는 16-bit다. 그러나 메모리 뱅크의 분류는 8그룹으로 배가 되고 있어 액세스는 현재와 변하지 않을 가능성도 있다. 메모리 모듈은 삼성의 설명에서 현행과 모듈형은 유사하다. Micron의 슬라이드는 DDR5에서 메모리 모듈도 기술 쇄신이 되는 것으로 알려졌다.

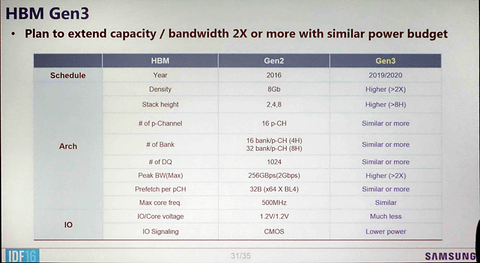

2TB/s 이상의 초광대역 메모리를 목표로 하는 HBM3

광대역 메모리 HBM은 AMD가 "Radeon R9 Fury(Fiji)"에서 "HBM1"을 채용하고 NVIDIA가 Pascal(파스칼) "Tesla P100(GP100)"에서 "HBM2"를 채용했다. 아직 갓 출범한 HBM이지만 벌써 HBM3의 규격 책정이 진행되고 있다. 이쪽도 타깃으로 하는 시기는 2019년부터 2020년.

HBM2에서 전송 속도는 2Gbps지만 HBM3는 2배 이상으로 오른다. HBM을 4스택으로 사용하는 하이엔드 GPU의 메모리 대역은 2TB/s 이상이 되는 계산이다.

HBM2는 다이의 용량도 8G-bit(ECC를 포함하면 9G-bit)로 이것도 2배 이상의 증가를 목표로 한다. HBM2는 코어와 I/O의 전압이 1.2V지만 HBM3는 이보다 대폭 낮아지고 소비 전력을 억제할 전망이다.

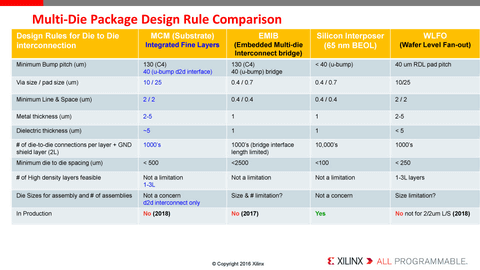

HBM은 고성능화와 함께 저가화 움직임도 활발해지고 있다. JEDEC은 HBM1 릴리즈 전부터 이미 저가 HBM에 대한 패스를 검토하고 있다. 현재의 HBM은 기본 논리 다이와 실리콘 Through Silicon Via(TSV) 인터포저를 필요로 하기 때문에 고비용이 되고 있다. 저가 HBM에서는 우선 논리 다이의 필요를 없애고, 인터페이스 폭을 현재 1024-bit에서 512-bit로 낮춘다. 배선 밀도를 낮춤으로써 최종적으로는 실리콘이 아닌 유기 재료 인터포저에서 서포트할 수 있도록 하는 것이 목적이다. 이 밖에 Hot Chips에서는 HBM의 패키지 기술의 저비용화 가능성도 제시됐다.

참고로 HBM은 인텔도 채용을 검토하고 있다고 IDF에서 시사했다. 다만 채용이 HBM2와 HBM3 어느 세대일지는 모른다고 한다.

LPDDR4X에서 LPDDR5로 진화하는 모바일 DRAM

LPDDR에서 메모리의 진화는 LPDDR4X와 LPDDR5의 2단계가 된다. DDR5와 비교하면 움직임이 빠른 생산은 LPDDR4X로 올해(2016년), LPDDR5는 2018년 전망이다.

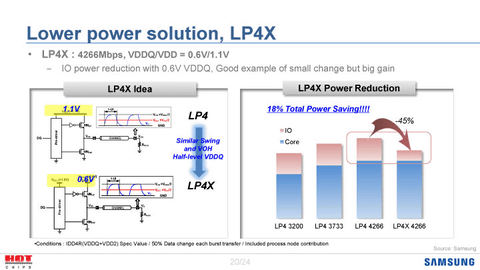

모바일 LPDDR4를 저전력화한 LPDDR4X는 삼성이 강력히 추진하고 있다. LPDDR4X의 핵심은 코어 전압(VDD)은 바꾸지 않고, I/O 전압(VDDQ)만 낮추는 점이다. I/O 전압을 LPDDR4의 1.1V에서 0.6V로 낮추고 I/O 전력이 40% 가량 줄어든다.

LPDDR4X의 타깃으로 하는 최고 주파수는 4.266Gbps. 이를 LPDDR4의 3.2Gbps와 같은 수준의 전력으로 실현한다.

LPDDR4X는 삼성이 선행하고 있지만 다른 DRAM 벤더도 지원할 예정이다. 어느 JEDEC 관계자는 "LPDDR4X는 LPDDR4를 제조하는 업체들은 모두 제조할 것이다. 사용자도 이미 복수가 움직이고 있다. 멀티 제조 벤더에서 멀티 유저의 확고한 규격이다" 라고 한다. 실제로 JEDEC 컨퍼런스에서는 Micron이 LPDDR4X의 설명을 하고 있었다.

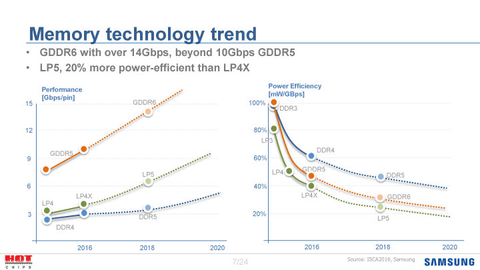

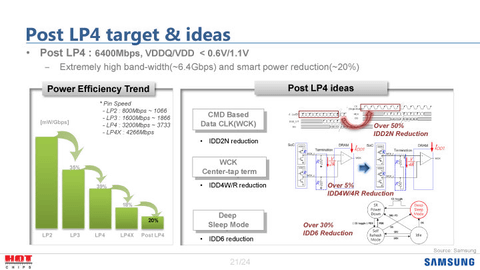

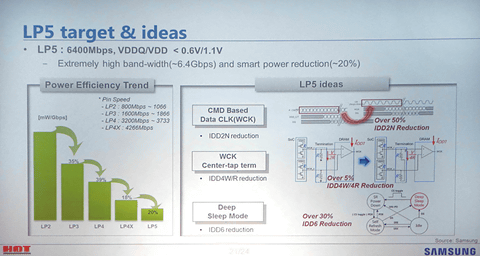

LPDDR5에 대해서는 IDF에서 인텔의 Findley가 JEDEC에서 책정의 최종 단계에 들어섰다고 설명했다. 내년(2017년)에는 JEDEC이 LPDDR5 사양을 공개, 2018년 타임 프레임에는 LPDDR5이 시장에 등장할 것이라고 한다. LPDDR5의 타깃 전송 속도는 6.4Gbps, I/O 전압은 0.6V이하로 전력 절약 기능의 강화로 LPDDR4X에 비해 20% 전력을 낮추겠다는 것이다.

그래픽용 고속 메모리 규격 GDDR6는 조기에

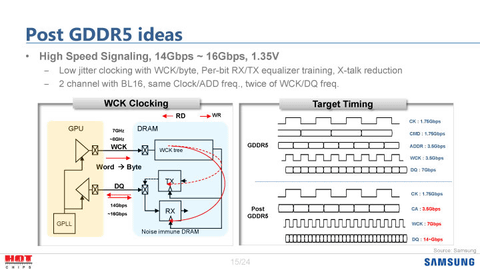

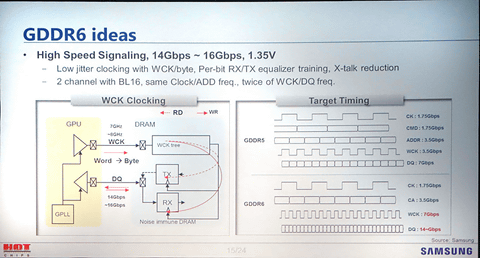

GDDR6는 현재의 GDDR5의 후계 메모리 규격이다. 타깃 전송 속도는 14~16Gbps로 GDDR5의 2배 전송 속도다. 256-bit 메모리 인터페이스의 미들레인지 GPU라면 500GB/s급 메모리 대역을 실현한다. 클럭과 주파수는 GDDR5의 상태로 전송 속도를 배로 한다. GDDR6에 대해서는 JEDEC의 규격화를 앞당기고 어느 JEDEC 관계자는 내년(2017년)에 등장한다고 한다.

이 배경에는 기업 정치도 있다. GDDR5 후계 메모리는 Micron이 GDDR5X를 제품화, NVIDIA가 GeForce GTX 1080(GP104)에 채용했다. GDDR5X도 JEDEC 표준이지만 LPDDR4X와 달리 Micron 이외의 벤더가 제품화할 가망이 없다고 한다. 삼성 등 대항 벤더는 GDDR6에 주력하고 있으며 현재는 GDDR5 후계 메모리가 2개로 갈라진 상황이다.

출처 - http://pc.watch.impress.co.jp/docs/column/kaigai/1015892.html