Bitsandchips.it가 애플이 2017년부터 2018년에 발매하는 차세대 아이맥과 맥북에 커스텀 x86 SoC을 채용하는 것을 검토하고 있다고 보도 했습니다.

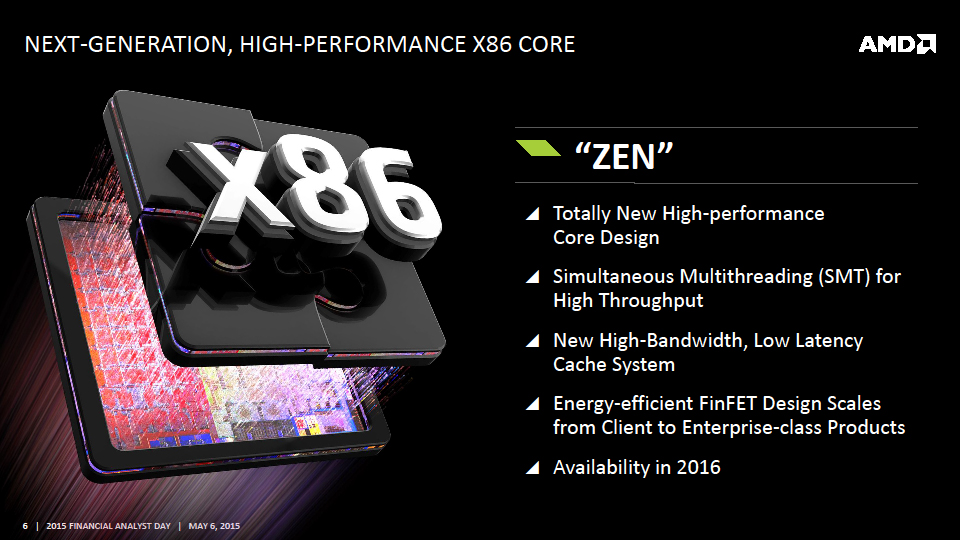

SoC는 System-on-a-chip의 약어로 하나의 반도체 칩 위에 필요한 일련의 기능(시스템)을 집적하는 방식을 뜻하며 애플의 커스텀 x86 SoC 파트너로 거론되고 있는 것이 AMD이며 2016년부터 2017년에 등장하는 AMD의 차세대 x86 아키텍처 Zen(젠)을 애플이 채용한다는 내용 입니다.

또한 애플과 AMD는 2011년에 애플이 맥북에어에 AMD 프로세서의 채용을 검토한 것으로 드러나고 있는데 그 당시는 공급량 등의 문제로 실제 채용까지는 이르지 못하고 보류되었다고 합니다.

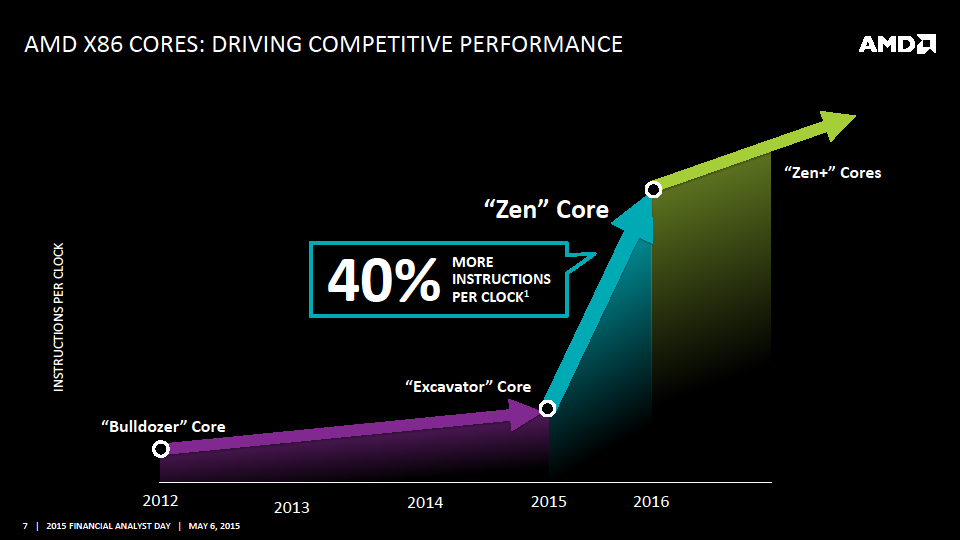

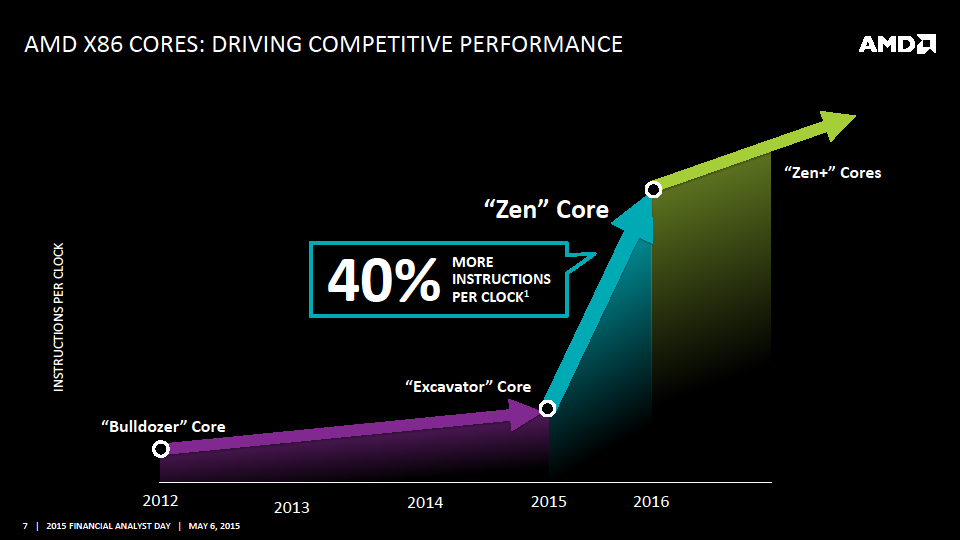

한편, AMD가 내년에 공식 발표를 예정하고 있는 차세대 아키텍처 Zen(젠)은 프로세서의 IPC가 40% 향상 될 것이라고 밝혀 기대를 모으고 있습니다.

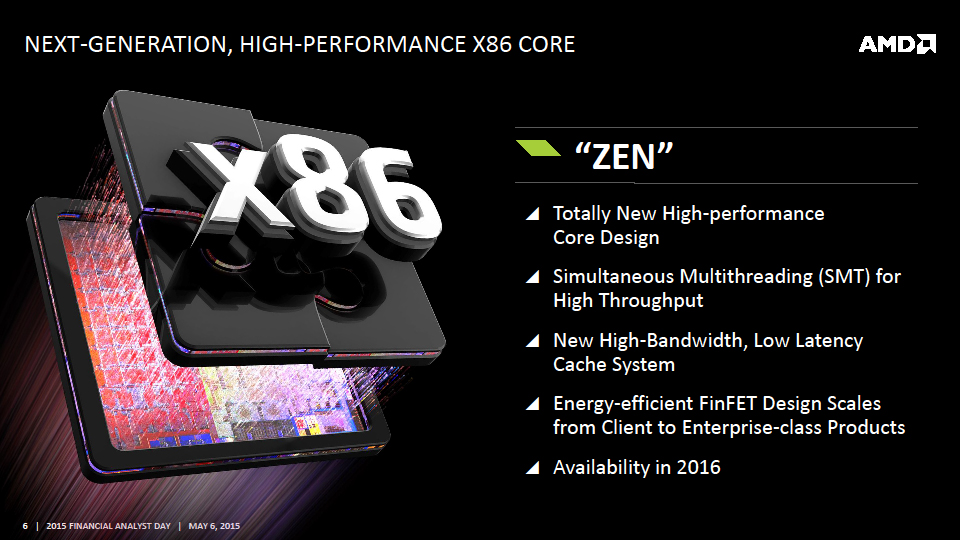

[ 차세대 AMD 젠 아키텍처 개요 ]

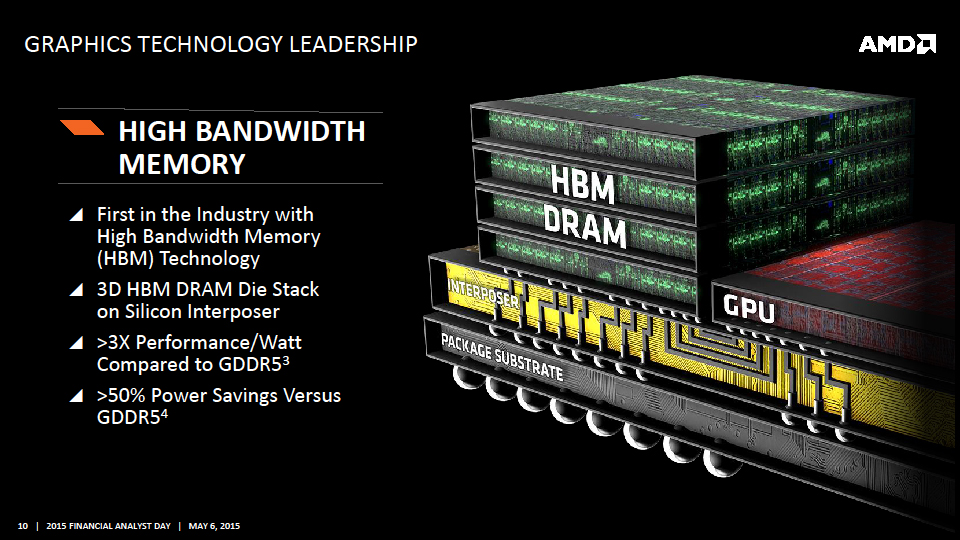

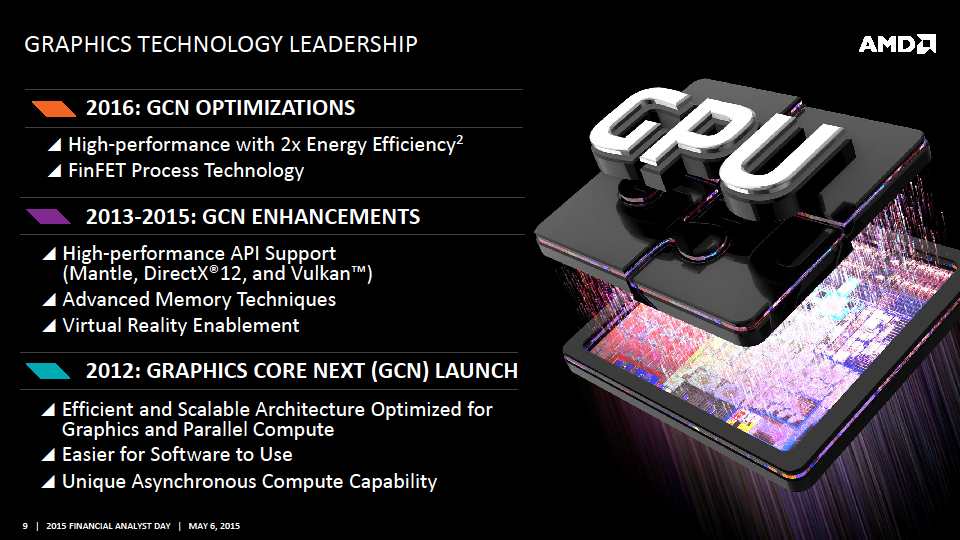

AMD는 차세대 x86 CPU "젠(Zen)"과 ARM CPU "K12"를 양축으로 전개한다. Zen은 현재의 불도저(Bulldozer)계 CPU 코어 "Excavator(엑스카베이터)"보다 40%나 클럭당 실행 성능이 높아진다. 또 GPU에는 차세대 광대역 메모리 기술 "HBM(High Bandwidth Memory)"을 타사보다 앞서 채용한다.

앞으로 몇 년간 이 회사는 신 아키텍처와 신 기술의 러시가 진행된다. 강력한 신규 CPU 코어와 GPU 코어를 기둥으로 게임과 가상 현실 등의 몰입형 플랫폼, 그리고 데이터 센터와 같은 시장을 개척한다는 전략이다.

또 PlayStation 4(PS4)과 Xbox One에서 성공한 세미 커스텀 형의 비즈니스도 확산하고 있는 것으로 밝혔다. AMD는 지난 몇 년간 전통적인 PC 플랫폼 이외의 시장 개척에 힘을 쏟아 왔고 신규 CPU 코어에 의해서 그 전략이 점차 구체화 되고 있다.

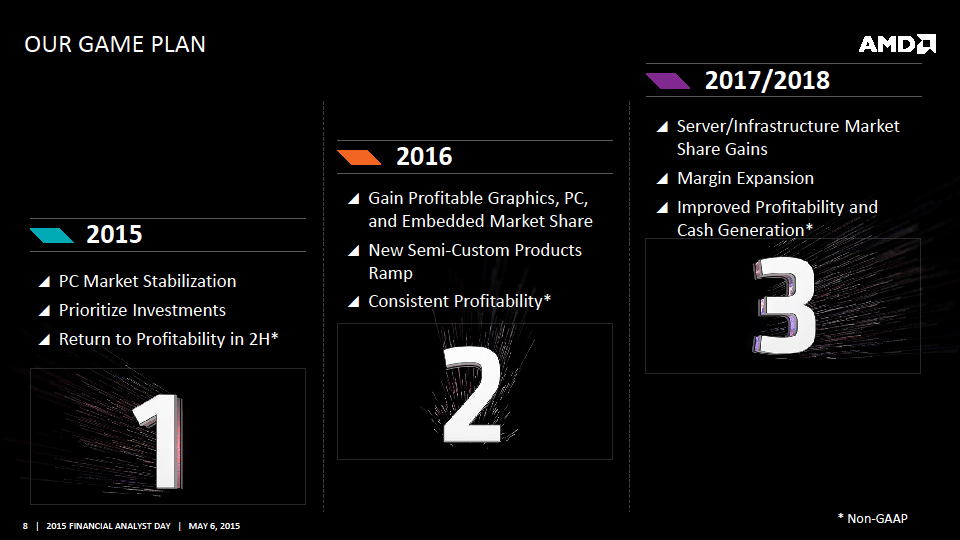

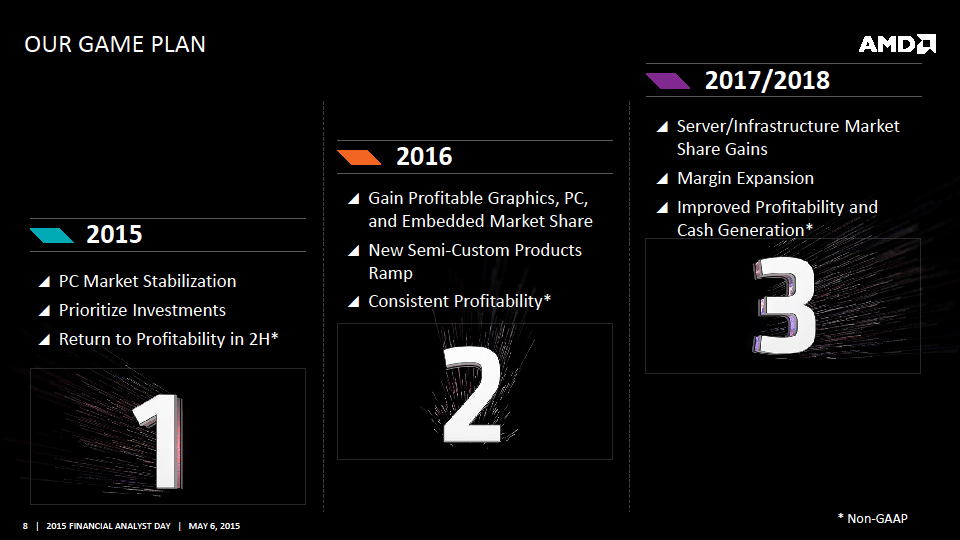

AMD는 미국 뉴욕 증권 거래소 나스닥(NASDAQ)에서 개최한 "2015 FINANCIAL ANALYST DAY"에서 동사의 기업 전략 전환과 제품 로드맵의 쇄신을 발표했다. 첫머리에 등장한 AMD의 Lisa Su(리사수)(President and Chief Executive Officer, AMD)는 동사의 비즈니스 이행이 순조롭게 진행되고 있으며 전통적인 PC 비즈니스 외의 엔터프라이즈, 배치, 세미 커스텀 매출이 2014년 40%에 이른 것을 설명. 이들 시장 확대로 이후 동사의 사업이 급속하게 상승세를 탈 것이라 밝혔다.

이 회사가 이번에 발표한 제품 로드맵은 이러한 기업 전략에 따르고 있다. 강력한 CPU코어의 투입에 포커스하여 플랫폼을 단순화하고 확장 가능하게 한다. 그래서 내년(2016년)에는 새로운 CPU 코어 젠을 탑재한 CPU 제품을 하이엔드의 FX 시리즈로 출시한다.

젠은 현재의 Bulldozer(불도저)계 마이크로 아키텍처의 CPU코어가 아니라 완전히 새로운 설계의 코어다. 올해의 APU "카리조(Carrizo)"에 탑재되는 엑스카베이터 코어보다 클럭당 명령 실행 성능 IPC(Instruction-per-Clock)가 40%나 높아진다고 한다. Bulldozer계는 스레드에 정수 연산 파이프가 2개지만 젠에서는 3개 이상으로 되는 것은 확실할 것.

또, 젠은 AMD의 CPU에서는 처음으로 SMT(Simultaneous Multithreading)를 지원 한다는 것을 AMD의 기술 전략을 총괄하는 마크 페이퍼 마스터(Mark Papermaster) Senior Vice President and Chief Technology Officer에 의해서 밝혀졌다. SMT는 인텔이 Hyper-Threading으로 채용하고 있으나 젠의 탑재에 대해서는 밝혀지지 않았다. 또 캐시 시스템을 갱신해 광대역이며 동시에 낮은 레이턴시 캐시 계층을 구현하는 것도 공표, FinFET 3D 트랜지스터 기술을 제조 공정 기술에 사용함으로써 전력 효율이 크게 개선된다고 설명했다.

AMD는 지난해(2014년) 5월 젠과 함께 고성능 ARM 코어 "K12"을 개발하고 있는 것도 밝혔다. K12는 2017년에 투입되며 서버 및 성능이 요구되는 임베디드 시장을 위한 제품이다. 젠의 개발 노하우가 K12에도 활용 될 것으로 보인다. AMD의 고성능 CPU는 커스텀 회로 설계를 다용하는데 K12도 그러한 설계가 될 것으로 예상된다.

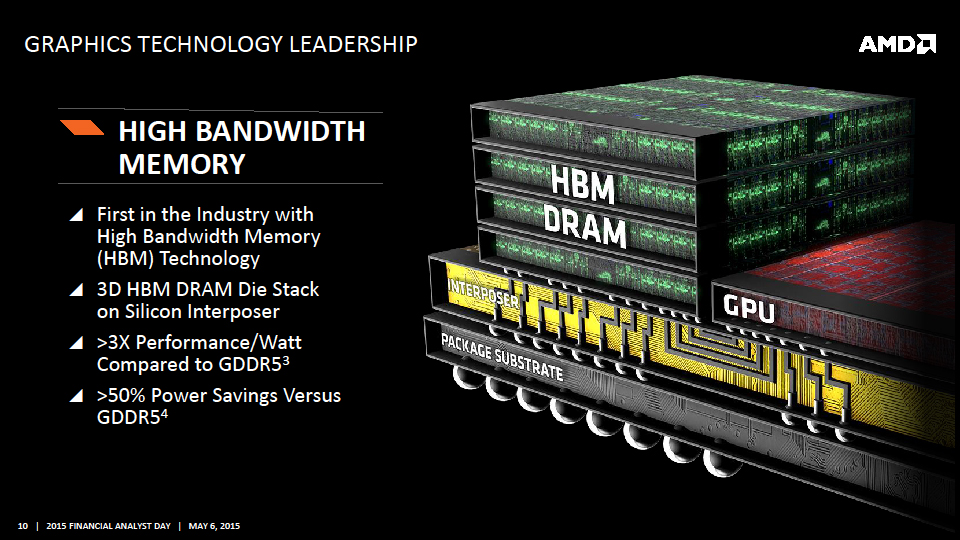

GPU는 광대역 메모리 기술 HBM(High Bandwidth Memory,SK 하이닉스)를 채용한 제품이 올해 중반에 발표되는 것도 확인됐다. HBM은 다이(반도체 본체)를 적층 하는 스택 DRAM 기술로 500GB/sec 이상의 메모리 대역을 GDDR5 보다 훨씬 낮은 소비 전력으로 실현한다. 이 회사는 HBM을 우선 GPU의 GDDR5 대체 그래픽 메모리로 채용한다고 한다.

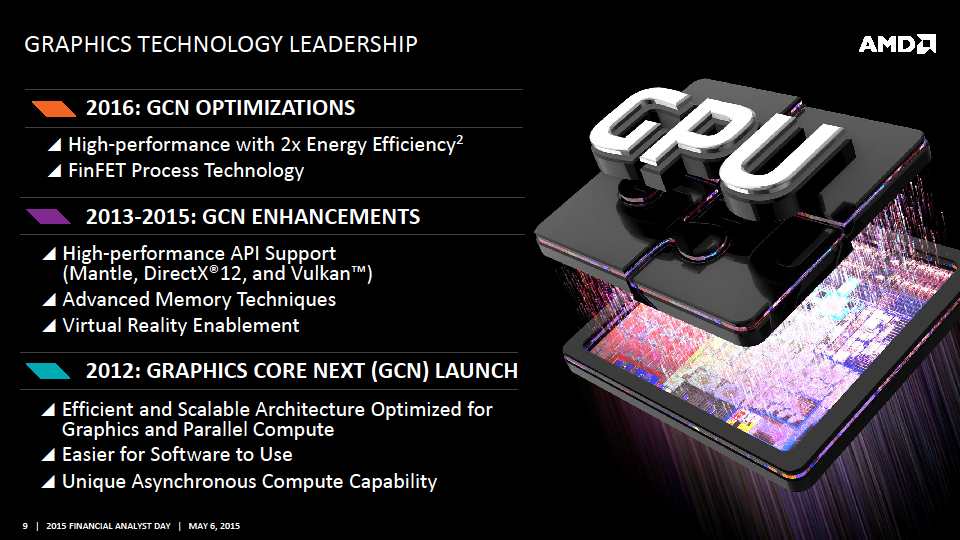

GPU 코어는 내년(2016년)에는 현행 GCN(Graphics Core Next)을 개량한 GCN 3.0으로 이행, FinFET 3D 트랜지스터 프로세스 기술로 이행하고 전력 효율을 2배로 높이겠다고 밝혔다. 또 가상 현실에 대한 최적화도 하겠다고.

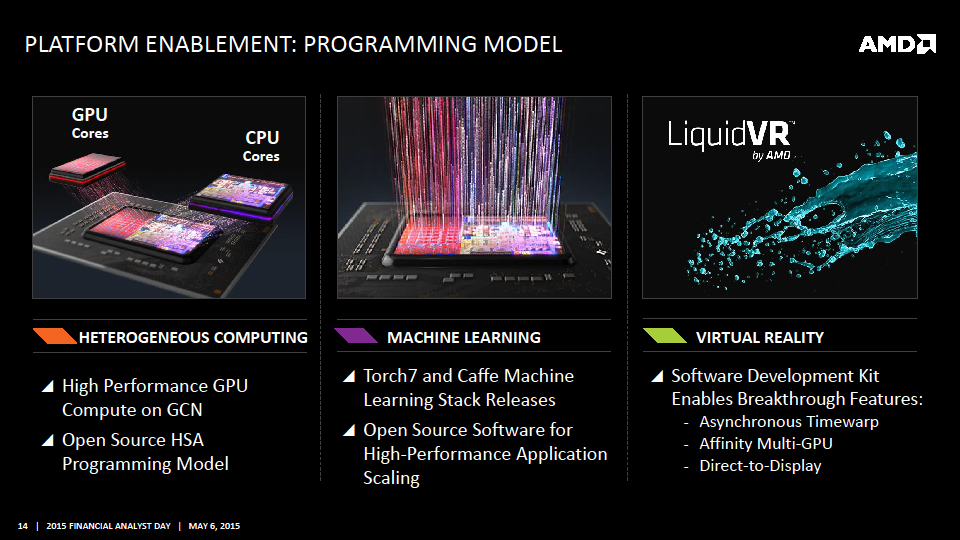

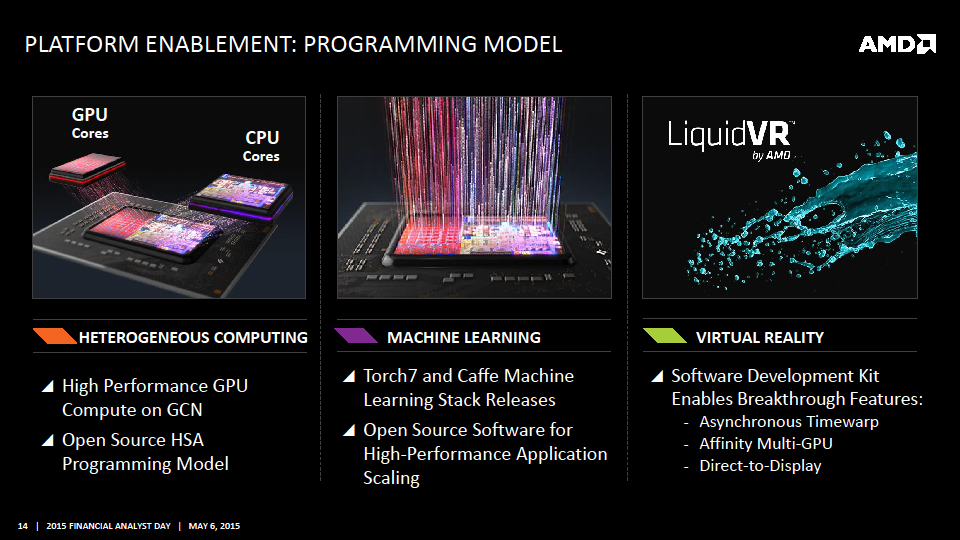

CPU 코어와 GPU 코어의 개량에 의해서 AMD는 앞으로 APU(Accelerated Processing Unit)의 전력 효율도 높인다. 2020년까지 현재보다 25배의 전력 효율 향상을 목표로 한다. 또 CPU와 GPU를 통합한 HSA(Heterogeneous System Architecture)의 프로그래밍 모델도 확충한다. 머신 러닝의 시장에도 포함할 것이라 AMD는 생각한다.

제품 로드맵에서는 지난해 5월 발표한 x86과 ARM의 호환 "칩 설계 프레임워크" "Project SkyBridge(스카이브릿지)"가 취소된 것으로 밝혀졌다. 이는 x86과 ARM의 플랫폼 호환 요구 자체가 낮다고 AMD는 설명한다.

무엇보다 스카이브릿지의 본질은 소켓과 마더보드와 같은 차원뿐만 아니라 SoC(System on a Chip) 내부 호환에 x86과 ARM 두 아키텍처의 SoC의 설계 호환성을 높인다는 점이다. 이 점이 젠과 K12 세대로 지속될지는 밝혀지지 않았다.

스카이브릿지는 20nm 프로세스로 올해(2015년) 제조 될 예정이었다. 그러나 20nm는 IP를 설계해 봤지만 CPU에는 이점이 적은 것이 밝혀지면서 AMD는 메인 스트림 제품에는 20nm를 채용하지 않기로 했다고 한다. 현재의 제품 로드맵에서 28nm의 평면 트랜지스터 프로세스에서 14/16nm의 FinFET 3D 트랜지스터 프로세스로 점프할 계획이다.

스카이브릿지의 취소는 이 회사의 설계 자원을 집중시키고 플랫폼을 심플화하며 제품 라인을 정리한다는 점에서는 효과가 높다. 또, 기업과 내장, 세미 커스텀에 맞춘다는 회사의 전략에도 부합한다. 결과적으로 AMD의 로드맵은 단단한 것이다.

랩터 인터내셔널 - http://raptor-hw.net/xe