ESSDERC 2016) 인텔과 STMicro의 SoC용 초고속 레귤레이터

대규모 마이크로 프로세서나 대규모 SoC(System on a Chip) 등은 실리콘 다이를 수많은 전원 도메인으로 구분하고 공급 전압을 동적으로 조정하는 경우가 많다. 작동 성능과 소비 전력의 균형을 최적의 포인트로 유지하기 위해서다.

전원 도메인에 일정 전압의 전력을 공급하는 레귤레이터는 프로세서나 SoC 등의 실리콘 다이에 가까운 위치에 배치하는 것이 바람직하다. 레귤레이터와 부하(프로세서나 SoC 등의 내부 회로)의 거리가 길면 전압과 전류가 쓸데없이 변동하는 것과 동시에 전압을 최적의 값으로 조정하기 위한 시간(응답 시간)이 길어지기 때문이다.

그래서 레귤레이터의 최적의 레이아웃은 프로세서나 SoC 등과 같은 실리콘 다이, 즉 온 칩임을 알 수 있다. 혹은 같은 패키지에 근접해 내장한다. 이러한 레귤레이터 회로는 "IVR(Integrated Voltage Regulator)" 이라고 부르는 경우가 많다.

9월 12일~15일 스위스에서 개최된 유럽 최대의 반도체 국제 학회 "ESSDERC/ESSCIRC" 에서는 인텔의 공동 연구 팀과 STMicroelectronics의 공동 연구 팀이 각각 새로운 IVR 기술을 발표했다. 모두 부하 변동에 신속하게 대처하면서 목표 전압 변화에 신속하게 대응하며 고속의 응답을 특징으로하는 온 칩 레귤레이터(DC-DC 컨버터)다.

부하 변동에 대한 응답 시간을 2.5분의 1로 단축

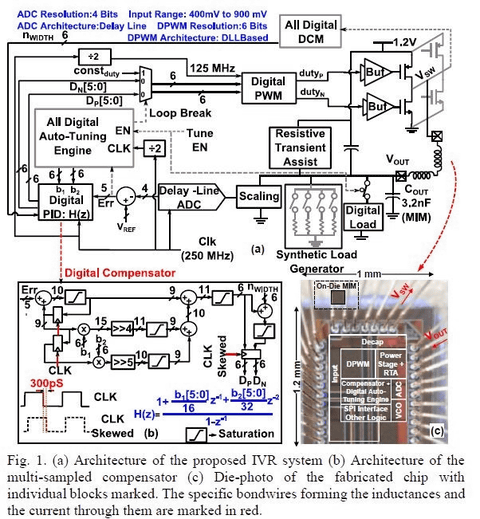

인텔은 미국의 Georgia Institute of Technology와 공동으로 IVR 기술을 개발하고 그 성과를 발표했다.(ESSCIRC, C3L-J) 마이크로 프로세서와 온 칩 혹은 동일 패키지에 포함시키는 것을 상정하고 개발했다.

개발한 IVR(DC-DC 컨버터)의 기본 구성은 인덕터와 캐패시터, 스위칭 FET(PWM 출력)으로 구성하는 일반적인 것. 단, 인덕터와 캐패시터를 소형화하기 위해서 스위칭 주파수를 125MHz로 매우 높이고 PWM 출력 회로 및 제어 회로 등을 풀 디지털로 설계했다. 또 수동 소자의 상수 변화를 신속하게 보상하기 위해 클럭 주파수가 250MHz로 매우 높은 디지털 회로를 탑재했다.

또 패키지 본딩 와이어의 일부를 인덕터에 유용함으로써 인덕터의 추가를 생략했다. 본딩 와이어에 의해 인덕턴스는 약 12nH다. 캐패시터는 다른 다이로 구성된 MIM(금속/절연체/금속) 캐패시터를 적층 했다. MIM 캐패시터의 용량은 3.2nF.

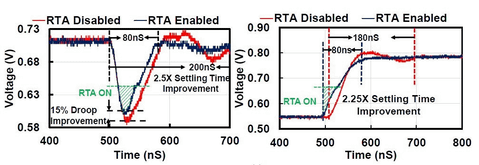

개발한 실리콘 다이를 실제로 측정하고 평가한 결과 응답의 고속성을 확인했다. 부하 변동에 대한 회복 시간(설정 시간)은 2.5분의 1로 단축됐다. 또, 전원 전압 강하의 폭은 15% 정도 작아졌다. 목표 전압의 변화에 대한 회복 시간(설정 시간)은 2.25분의 1로 단출할 수 있었다.

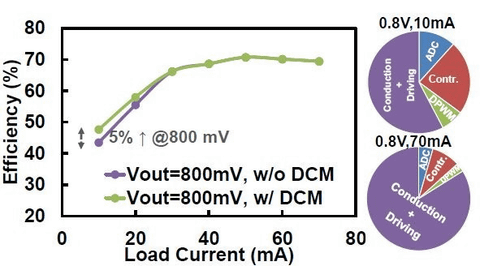

또한 가벼운 부하의 변환 효율을 5%(5 포인트)정도 향상되었다. 단 최대 효율은 71%로 그렇게 높다고는 말할 수 없다. 변환 효율의 값 자체는 개량이 간절히 요구된다.

DC-DC 컨버터를 내장한 64bit RISC 프로세서

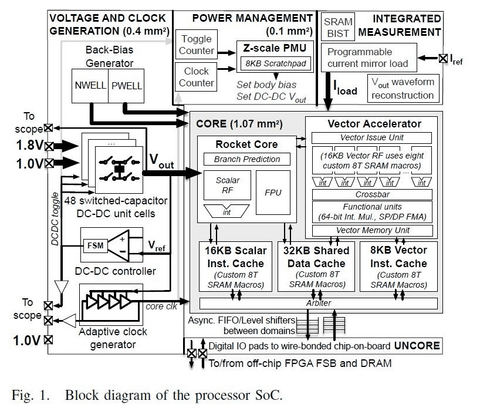

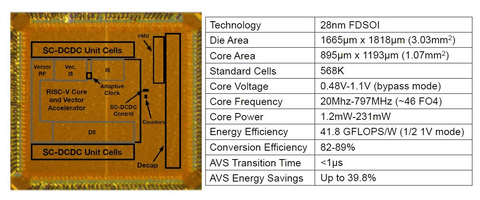

STMicroelectronics는 미국의 University of California, Berkeley(UCB)과 공동으로 개발한 IVR(DC-DC 컨버터)를 내장한 "RISC-Ⅴ 프로세서" SoC를 발표했다.(ESSCIRC, B2L-G)"RISC-Ⅴ는 UCB가 주도하고 추진 중인 오픈 아키텍처의 프로세서 개발 프로젝트다. 프로젝트의 일환으로 DC-DC 컨버터를 내장하는 프로세서를 개발하고 이에 STMicroelectronics가 제조 측면 등에서 협력한 것으로 알려졌다.

내장한 DC-DC 컨버터의 기본 구성은 스위치드 캐패시터(충전 펌프)다. 스위치드 캐패시터는 수많은 미세한 캐패시터와 스위치를 조합함으로써 다양한 정전압을 출력한다. 장점은 반도체 프로세스에서는 서투른 인덕턴스를 사용하지 않기 때문에 CMOS 프로세스와의 호환성을 유지하기 쉽고, PWM 출력의 스위칭 전원에 비해 노이즈가 비교적 작은점 등이다. 약점은 출력 전압의 변경이 연속적이 아니라 캐패시터의 최소 용량으로 정해지는 이산적인 값을 취하는 것, 그리고 큰 전력을 내지 못하는 것이다.

또한 출력 전압이 이산적인 값을 취할 것이라고는 하지만 프로세서나 SoC 등의 전압 스케일링에는 충분한 입도다. 이에 대해 전력을 내지 못한다는 약점은 상당한 문제로 예컨대 서버, 데스크탑 PC, 노트 PC 등의 메인 프로세서에는 적용할 수 없다고 봐야 할 것이다. 모바일 기기, 그것도 배터리 구동이 전제인 저전력 프로세서가 스위치드 캐패시터를 살릴 수 있는 용도다. 이번 "RISC-Ⅴ 프로세서"도 소비 전력은 CPU 코어 부분에서 최대 231mW로 매우 낮다.

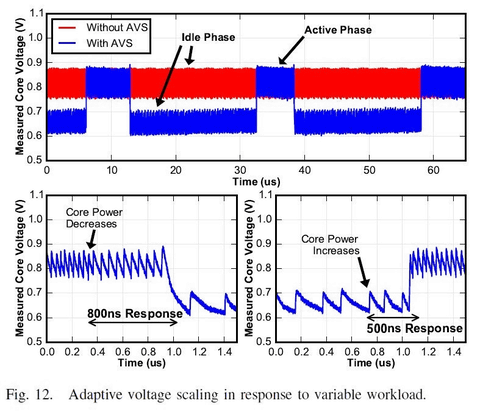

개발한 실리콘 다이에서 DC-DC 컨버터 성능을 평가한 결과 상당히 좋은 결과를 얻었다. 예를 들면 CPU 코어의 전원 전압을 부하에 맞추어 변화시킨 결과 응답 시간은 전압을 낮출때 800ns, 전압을 올릴때가 500ns였다. 전원 전압을 일정하게 한 경우에 비해 소비 전력은 39.8%절감할 수 있었다. 또 DC-DC 컨버터의 변환 효율은 최대 88.7% 였다.

'글로벌 IT 뉴스' 카테고리의 다른 글

| 애플의 아이폰도 인텔 인사이드가 되는가 (0) | 2016.10.11 |

|---|---|

| 서피스 키보드에 이어 서피스 마우스도 등장 (0) | 2016.10.07 |

| AMD, 비즈니스 데스크탑을 위한 7세대 APU 출하 (0) | 2016.10.07 |

| CEATEC 2016) 샤프가 IGZO 27형 8K 디스플레이 전시 (0) | 2016.10.07 |

| 구글 홈 발표, 아마존 에코에 대항하는 홈 어시스턴트 (0) | 2016.10.05 |