헤테로지니어스 멀티코어 구성의 아이폰7 A10 프로세서

패키지 기술의 대혁신이 된 iPhone 7의 A10

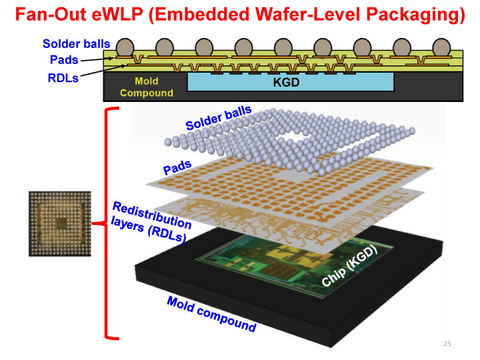

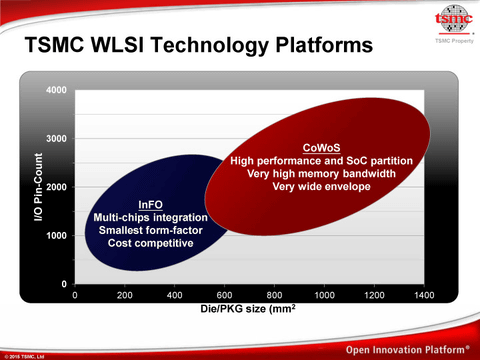

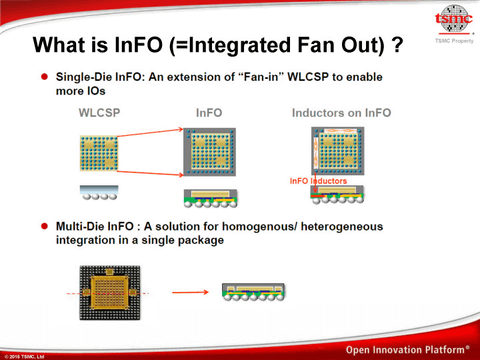

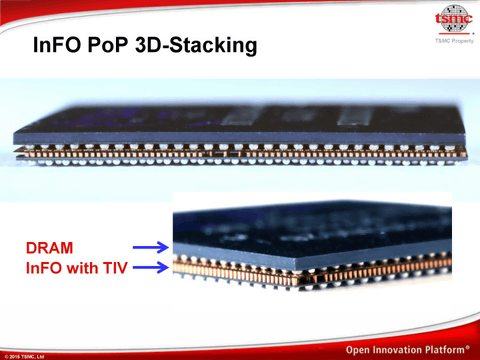

Apple iPhone 7의 모바일 SoC "Apple A10 Fusion"은 반도체 세계에서는 하나의 이정표 칩이다. 그것은 패키지 기술의 혁신이라는 점에서 큰 이정표가 있는 칩이기 때문이다. A10이 채용한 "Fan-Out Wafer Level Package(FO-WLP)" 기술은 그만큼 큰 변화다. FO-WLP는 유기 기판을 사용하지 않는 새 패키지 기술로 패키지의 특성을 크게 향상시키고 패키지의 두께를 줄인다. 즉, 패키지만으로 성능 효율을 올리며 시스템의 평판화를 용이하게 한다.

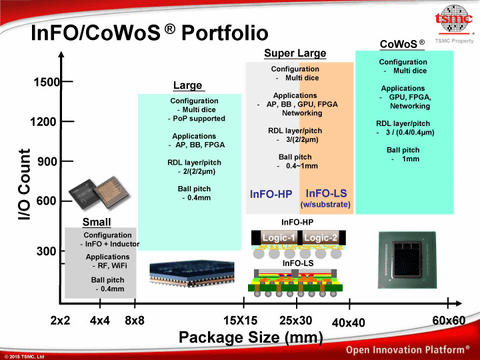

FO-WLP에서는 패키지에 매우 얇은 "Redistribution Layer(RDL)"을 사용한다. 그러나 기존의 칩 스케일 패키지 "WLCSP(Wafer Level Chip Scale Package)"와 달리 패키지 사이즈가 다이 사이즈와 동일할 필요가 없다. 핀 수가 많고 패키지 사이즈가 다이 사이즈보다 큰 칩에도 사용할 수 있고 응용의 폭이 넓다.

FO-WLP 기술은 두꺼운 서브 스트레이트가 없어지는 만큼 패키지의 두께(Z 하이트)가 얇아진다. 또, 배선이 줄어들기 때문에 배선 저항이 줄어 I/O 성능이 높아지고 소비 전력도 절감된다. iPhone 7의 A10을 제조하는 TSMC는 InFO-WLP 기술로 20% 패키지 두께를 줄이고 20% I/O 속도를 올리며 10%의 열 저감이 가능하다고 설명했다. A10은 칩 자체뿐 아니라 패키지를 통해서도 성능 향상과 전력 절감이 이루어지고 있는 셈이다.

A10에 대해서는 예전부터 FO-WLP 기술의 채용이 예상됐다. 이는 현재의 Apple A 시리즈를 제조하는 TSMC가 이 회사의 새로운 패키지 기술 "InFO WLP(Integrated Fan-Out Wafer-Level Package)"에 대형 고객이 추가 된 것을 밝히고 있었기 때문이다. TMSC는 지난해(2015년) 10월 파이낸셜 컨퍼런스 콜에서 2016년부터 InFO의 대량 생산이 시작되고 4분기에는 1억달러의 매출이 가능하다고 설명했다. 그래서 A10이 InFO WLP를 채용하는 것은 거의 예상됐다.

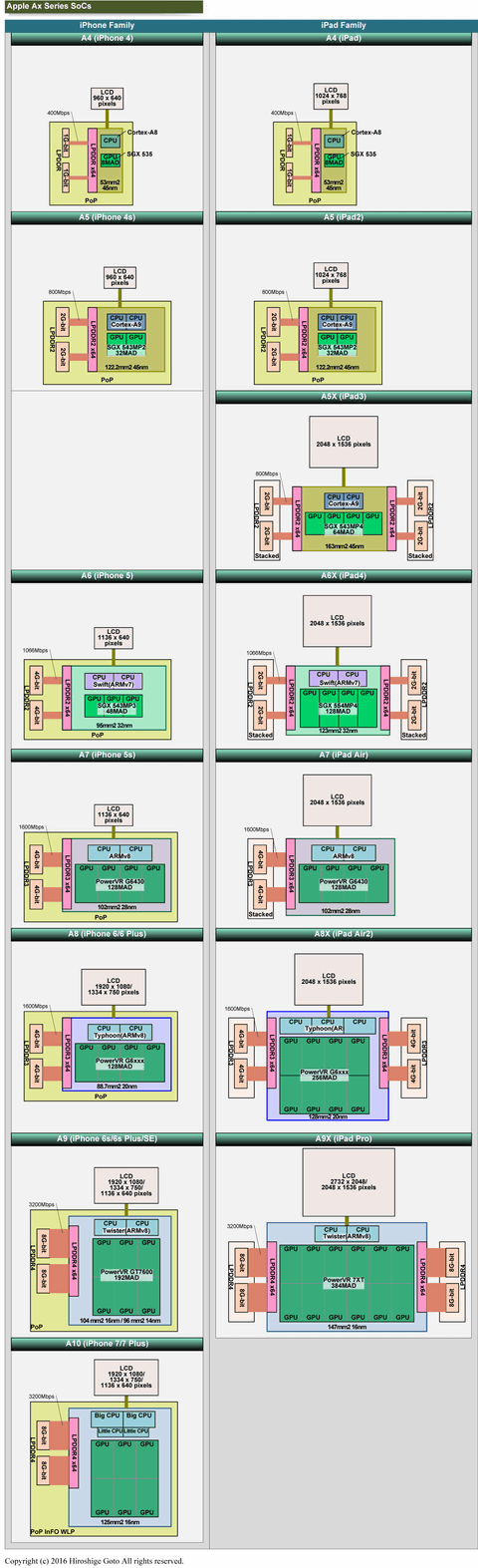

iPhone용 Ax 시리즈 SoC는 DRAM과 적층 한 PoP(Package On Package)에 탑재되고 있다. A10은 InFO 베이스의 POP.

반도체 칩으로 본 경우 A10의 최대 특징은 이 패키지 기술이다. iPhone은 지금까지도 여러가지 다양한 기술의 견인차가 되어 왔는데 이번 iPhone 7에서는 FO-WLP 기술 구성을 견인한다. FO-WLP는 패키지 기술의 오랜만의 큰 변혁이며 앞으로 큰 물결이 될 것으로 예상된다. 또 반도체 산업적으로는 파운드리의 인 하우스 패키지로 이행하려는 움직임이다.

시스템적으로는 FO-WLP는 패키지의 Z 하이트를 감소시킴으로써 케이스의 박형화를 용이하게 한다. 스마트폰 안에서 최대 열원인 애플리케이션 프로세서 칩이 FO-WLP로 얇아지게 되면 스마트폰 자체를 더 얇게 하기가 쉽게 된다. Apple의 케이스 기본 디자인의 설계 사이클은 2년이어서 이번 iPhone 7은 케이스 크기 자체의 변화는 거의 없다. 하지만 향후 박형화를 기대할 수 있다. 이번에 이어폰 잭을 배제함으로써 물리적 I/O 포트적으로 평판화의 준비가 되고 있다.

big.LITTLE을 닯은 헤테로지니어스 멀티코어 구성 CPU 코어

A10 칩 아키텍처 상의 최대 하이라이트는 대형 CPU 코어와 소형 CPU 코어의 헤테로지니어스 멀티코어 구성으로 된 것이다. ARM의 "big.LITTLE" 아키텍처와 같은 대/소 코어의 조합을 이루고 있다. Apple의 발표에는 2개의 고성능 CPU 코어와 2개의 고효율 CPU 코어의 조합으로 알려졌다. 고 전력 효율의 CPU 코어는 고성능 CPU 코어의 5분의 1 소비 전력으로 작동한다.

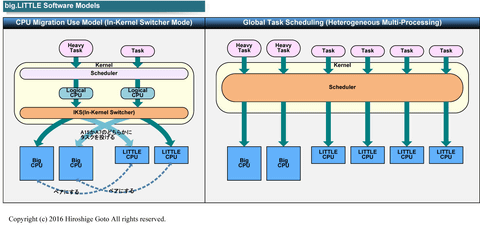

big.LITTLE을 닮았다는 것은 ARM의 big.LITTLE은 인터럽트 처리 등의 하드웨어 설계와 OS측의 스케줄러 확장 및 패치 등을 포함한 솔루션이기 때문이다. Apple은 ARM의 아키텍처 라이선스를 받아 CPU 코어 마이크로 아키텍처를 자체 개발하고 있다. OS도 자사 OS다. 그래서 대형 코어와 소형 코어 구성 제어는 Apple이 독자적으로 구성하고 있다고 보인다.

작업을 부하에 맞추어 대/소의 CPU 코어에 동적으로 나누어 고효율을 유지하는 것은 나름대로 어렵다. Apple은 파워 컨트롤러에 의해 자동적으로 제어된다고 발표시 설명하고 있다. 애플리케이션에서 CPU 코어의 대/소 제어는 물론 그 아래의 OS와 하드웨어가 어떤 제어를 하고 있는지는 아직 명확하지 않다. ARM의 big.LITTLE 소프트웨어 모델의 경우 OS의 스케줄러를 연결하여 대형 CPU 코어와 소형 CPU 코어를 쌍으로 전환하는 모델에서 태스크마다 CPU 코어를 배분하는 모델로 진화했다.

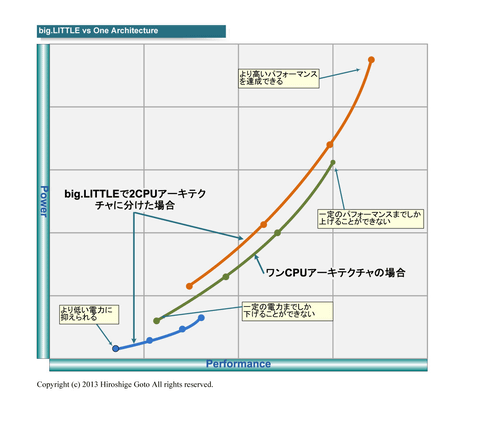

어쨌든 대형 코어와 소형 코어의 조합 이점은 분명하다. 그것은 CPU 코어 마이크로 아키텍처를 고성능과 저전력 각각에 적합화하는 것이다. 단일 CPU 코어에서 부하가 높을 때는 고성능을 발휘하고 저 부하시에는 전력을 철저히 억제할 필요가 있다. 그런 CPU 코어 마이크로 아키텍처와 회로 설계는 매우 복잡해진다. 인텔처럼 마이크로 아키텍처 레벨에서 회로 설계 프로세스 기술에 이르기까지 모든 영역을 튜닝하는 CPU 코어 개발을 할 수 없다면 고성능에서 저전력까지 단일 마이크로 아키텍처로 대응하기는 어렵다.

명령 병렬도가 높은 Apple의 독자 마이크로 아키텍처 코어

원래 Apple의 CPU 코어는 ARM 모바일 CPU 코어 가운데는 현격히 명령 병렬도가 높아 싱글 스레드 성능이 높다. 이는 ARM의 플래그십 CPU 코어 "Cortex-A72" 보다도 명령 병렬도가 높다. Apple은 저전력 CPU 코어 개발로 유명한 벤처 기업 P.A. Semi를 인수하면서 그 개발 진이 중심이 되어 Apple A 시리즈의 CPU 코어를 개발하고 있다. P.A. Semi 자체는 DEC의 Alpha 21064와 StrongARM의 개발자가 설립한 기업으로 회사가 개발한 Power 아키텍처의 CPU "PA6T"은 저전력이면서 4 내부 명령(uOPs) 처리에 5 실행 파이프와 2로드/스토어 파이프를 갖춘 파워풀한 코어였다.

Apple의 현재까지 CPU 코어는 64-bit(ARMv8) 명령 세트 아키텍처가 된 iPhone 5s의 Apple A7의 CPU코어 "Cyclone"이 베이스가 되고 있다고 보인다. Cyclone은 6uOPs 처리에서 정수 연산 파이프가 4개, 정수 곱셈 파이프가 1개, 나눗셈 파이프가 1개, 로드/스토어 파이프가 2개로 모바일 CPU 코어에서는 최대급에 파워풀한 CPU 마이크로 아키텍처다.

비교하면 Qualcomm이 Snapdragon 820 이후에 탑재되어 있는 자사 개발의 코어 "Kryo"가 5uOPs의 폭, Samsung의 M1이 4 명령 디코딩 3 정수 연산, NVIDIA의 Denver는 명령 해독기는 2명령이지만 일단 디코딩 한 명령에 최적화 스케줄링을 하여 최대 7uOPs의 병렬 실행이 가능하다. 이들과 비교해도 Apple의 CPU 코어 마이크로 아키텍처는 파워풀하다. 그만큼 논리 회로 규모가 크고 전력 절약화에 기술이 필요하다. 그래서 대형 코어와 소형 코어의 헤테로지니어스 멀티 코어화는 이치에 맞다.

iPhone의 메모리 대역 증가는 앞으로 다소 둔화

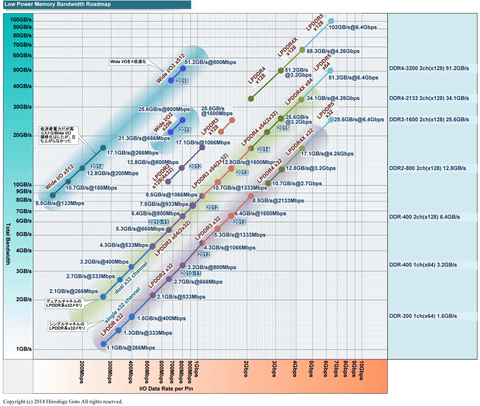

iPhone 7의 DRAM 메모리는 LPDDR4. 스택구조 DRAM 기술인 "Wide I/O 2"는 iPhone에 대한 채용을 놓쳐 적용되지 못했다. iPhone의 DRAM은 거의 2년 주기로 신세대 메모리 규격으로 이행해 왔다. iPhone 4의 A4까지 LPDDR에서 iPhone 4s의 A5에서 iPhone 5의 A6까지 LPDDR2, iPhone 5s의 A7에서 iPhone 6의 A8까지 LPDDR3, iPhone 6s의 A9과 iPhone 7의 A10의 LPDDR4.

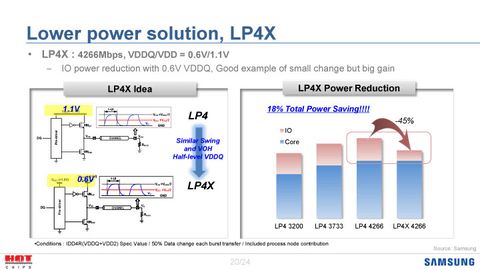

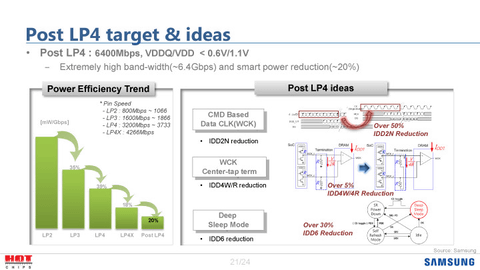

그러나 앞으로는 차세대 DRAM까지 간격이 생긴다. 차세대 LPDDR5는 사양 공개가 내년(2017년) 예정으로, 제품에 실제로 실리는 것은 2018년 타임 프레임이 될 전망이기 때문이다. 그래서 DRAM 업계에서는 중간계 LPDDR4X를 준비하고 있다. LPDDR4X는 코어 전압(VDD)는 LPDDR4과 같지만 I/O 전압(VDDQ)을 내린다. LPDDR4의 1.1V에서 0.6V로 I/O 전압을 낮추고 I/O 전력이 40% 가량 줄어든다. LPDDR4X는 LPDDR4의 3.2Gbps와 같은 수준의 전력으로 전송 속도 4.266Gbps를 실현한다. iPhone 8이 LPDDR4X를 채용한다면 메모리 대역은 피크에 34.1GB/sec을 달성하게 된다. 그러나 예전 같은 배가 성장은 될 수 없다.

이렇게 보면 스마트폰의 메모리 대역 성장은 그 동안 2년에서 2배의 속도보다 느려진다. 같은 메모리 인터페이스 폭이면 메모리 대역은 2년에 2배가 아니라 3년에 2배 정도의 페이스가 된다. 메모리 대역 성장 둔화는 모바일 SoC의 그래픽 성능에 영향을 미친다. 현재의 그래픽스 아키텍처는 메모리 대역에 크게 의존하기 때문에 메모리 대역은 핍박 받고 있다. 특히 PC 수준 이상의 고해상도인 iPad Pro에 대한 영향은 크다.

출처 - http://pc.watch.impress.co.jp/docs/column/kaigai/1022475.html

'글로벌 IT 뉴스' 카테고리의 다른 글

| ASUS, 12.5형 초경량 노트북 젠북3 발표 (0) | 2016.10.02 |

|---|---|

| ASUS, 11ac 대응 무선 LAN 라우터 RT-AC85U 발매 (0) | 2016.10.02 |

| 소니, HRA 노이즈 캔슬링 헤드폰 MDR-1000X 출시 (0) | 2016.09.21 |

| 웨스턴디지털, 세계 최초의 1TB SDXC 프로토 타입 발표 (0) | 2016.09.21 |

| 도요타가 인공 거미줄을 사용한 자동차 시트 개발 (0) | 2016.09.20 |