인텔 카비레이크G 연내투입 - HBM2, AMD GPU 통합

인텔 Kaby Lake-G의 의문

인텔은 적층 DRAM "HBM2"를 CPU 패키지로 통합한 "Kaby Lake-G"를 연내에 투입한다. 기존 eDRAM 버전 CPU와 마찬가지로 CPU 패키지 내에 HBM2의 DRAM이 탑재되고 있다. 다만 몇가지 큰 차이가 있다. 이미 소문으로 보도되고 있듯이 GPU 코어는 인텔의 내장 코어가 아닌 서드 파티의 디스크리트 GPU 다이다.

인텔이 AMD GPU를 CPU 패키지에 도입하는 이야기는 오래전부터 소문이 돌고 있었다. 보드 벤더 뿐 아니라 소프트웨어 개발자에게도 "서드 파티의 디스크리트 GPU와 HBM2"를 탑재하는 "G" 형식 번호의 Kaby Lake를 낸다고 설명하고 있었다고 한다. 사실 인텔은 지난해(2016년) 전반에 메모리에 대해서 업계 관계자에게 설명을 했으며 그 때는 HBM2의 채용은 2017년 중에는 하지 않을 예정이었다. 그 뒤 HBM2 채용 계획의 변경과 함께 AMD GPU의 채용과 Kaby Lake-G가 떠올랐다.

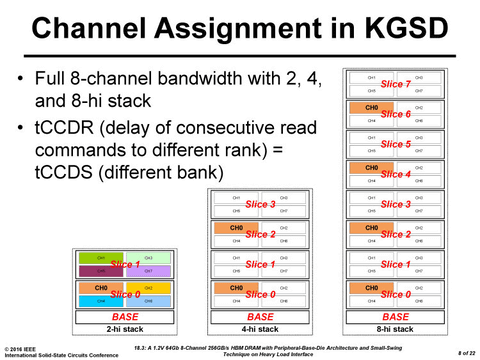

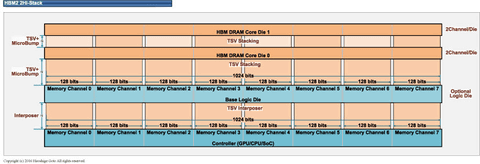

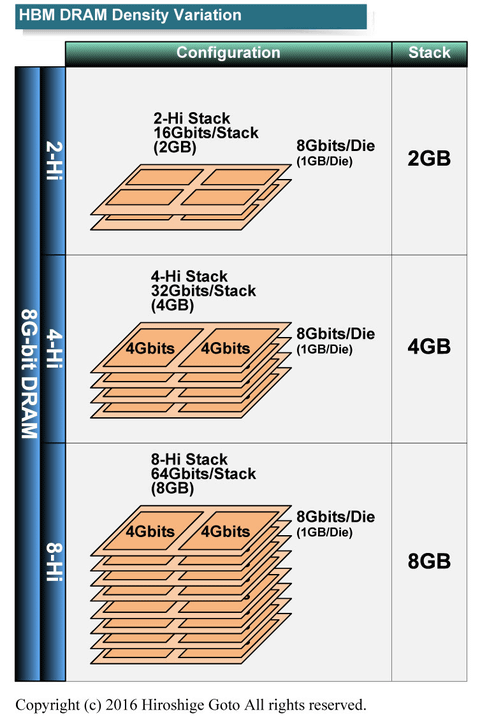

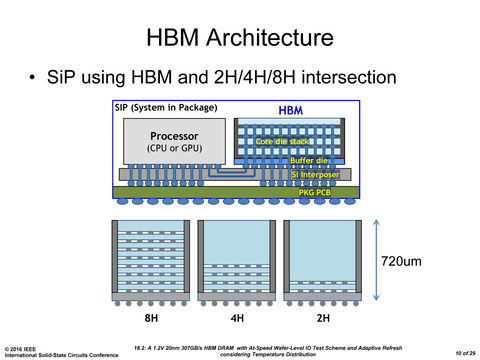

Kaby Lake-G의 패키지에는 쿼드 코어 버전 Kaby Lake 다이, AMD 디스크리트 GPU 다이, 그리고 HBM2가 1스택 탑재되고 있다. HBM2 스택의 다이 층수는 모르지만 HBM2는 풀 대역을 실현하려면 최저 2다이의 적층이 필요하므로 2다이나 4다이 중 하나라고 추측된다. 메모리 용량은 2GB 또는 4GB 어느 쪽이 된다.

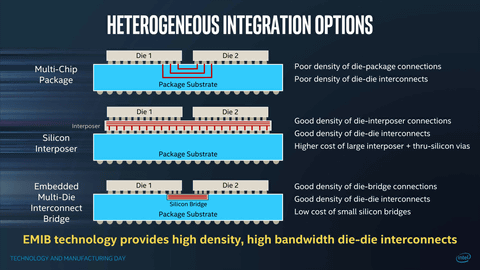

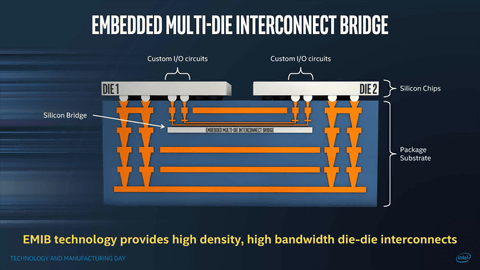

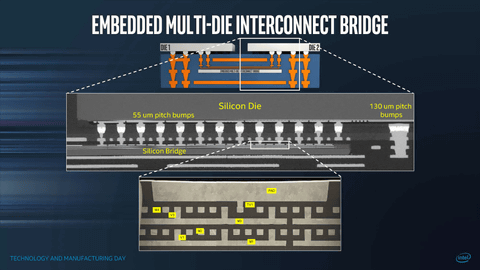

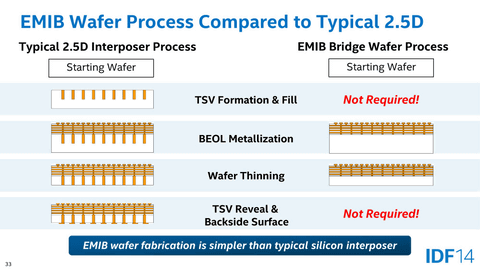

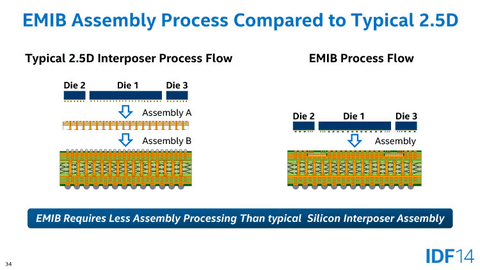

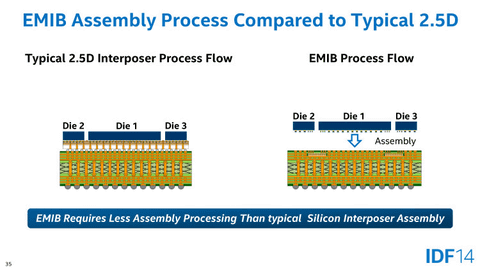

Kaby Lake 다이와 AMD GPU 다이의 사이는 온 패키지 PCI Express로 연결되어 있다고 보이고 AMD GPU 다이와 HBM2 스택의 사이는 인텔의 새로운 2.5D 솔루션 "Embedded Multi-die Interconnect Bridge(EMIB)"로 연결되어 있다고 본다. EMIB는 작은 실리콘 조각을 사용한 초고밀도 배선에 의해 기존보다 저비용으로 HBM2의 구현을 가능하게 한다.

인텔은 작년 상반기 단계에서는 2017년 중 HBM2의 도입은 생각하지 않았다. 2018년까지는 eDRAM 만이 인텔의 메인 스트림 PC에서 메모리 통합 솔루션이 될 예정이었다. 인텔 실리콘의 스케줄, HBM2 대응의 CPU 다이 투입은 2018년이기 때문이다. 그것을 AMD 다이를 도입하고 앞당기려는건 상당히 이례적인 일이다.

물론 CPU 제품 경쟁력 강화 때문이라고도 생각된다. 그러나 원래 Kaby Lake-G의 상대는 GPU 통합형 CPU인 AMD의 APU(Accelerated Processing Unit) "Raven Ridge(레이븐 릿지)" 세대인 셈인데 거기에 AMD GPU로 대항하는 이유를 알수없다. 그러나 이 제품화가 HBM2와 EMIB의 도입을 앞당기기 위해서라고 생각하면 납득이 간다.

EMIB는 이미 인텔 파운드리 서비스로서 제공되어 알테라 FPGA의 옵션으로 제공되고 있다. 그러나 가전 제품의 양산이라는 점에서는 아직 시작하지 않고 있다. 러닝 커브를 거두려면 먼저 양산을 시작해 EMIB와 HBM2의 플랫폼을 최대한 빨리 만드는 것이 좋다. Kaby Lake-G가 인텔의 패키지 기술의 선도적인 제품이라고 생각하면 여러가지 의문이 풀린다.

인텔의 2.5D 패키지 전략의 선도가 된 Kaby Lake-G

Kaby Lake-G에는 3가지의 큰 의미가 있다.

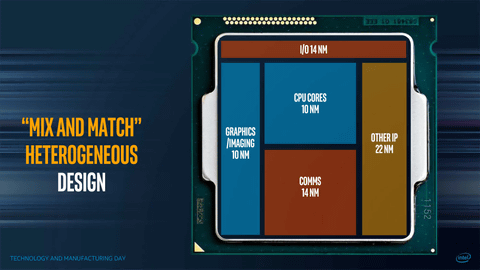

하나는 인텔이 "2.5D" 패키지 솔루션으로 본격적인 방향을 튼것. 2.5D 즉 1개의 칩 패키지에 여러 칩의 다이를 올린 타입의 적층 기술이다. 지금까지도 패키지에 복수 다이를 올린 "MCM(Multi-Chip Module)"은 인텔에도 다수의 제품이 있다고 생각할 수 있지만 이번 2.5D는 그것과는 얘기가 다르다.

이번 Kaby Lake-G는 HBM2를 채용하여 여러 광대역 인터페이스로 이어진다. HBM2는 1024-bit 대역의 인터페이스에서 2Gtps때 1스택당 256GB/sec의 대역을 실현한다. 고밀도 배선으로 이어 다이들을 광대역으로 접속하는 2.5D화가 이번의 흐름이다.

시작은 메모리의 HBM2지만 인텔은 커뮤니케이션 기능의 다이 등 메모리 이외의 다이간 CPU 다이와 광대역 접속한다. Kaby Lake-G는 그 선행 사례인 칩이다. 사실 인텔은 이러한 이기종 다이의 통합 계획을 발표하고 있다. 가까운 장래에 인텔의 칩은 복수의 다이가 고밀도 배선의 2.5D에 패키징 된 SIP(System in Package)가 일반적으로 될지도 모른다.

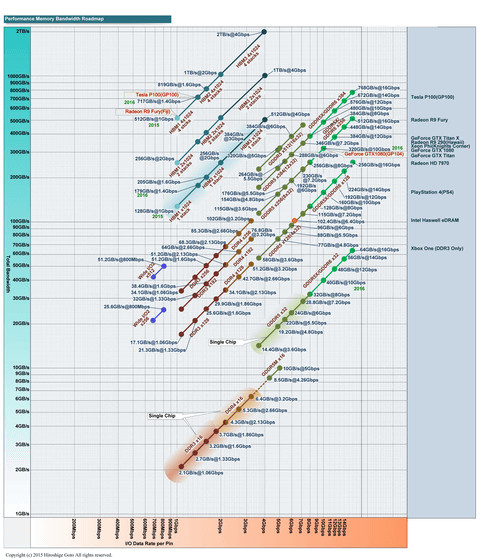

두번째는 인텔의 PC 프로세서가 메모리 대역 바인드에서 해방되는 것이다. 인텔과 AMD는 CPU 코어와 GPU 코어의 통합을 추진하고 있는데 현재의 DDR4 등의 메모리 모듈형 솔루션에서는 메모리 대역이 GPU 코어에 대해 모자르다. 그러나 CPU는 메모리 용량과 비용 증설성 면에서 이점이 있는 DRAM 모듈을 버리는 것이 어렵다. 디스크리트 GPU 같은 힘으로 메모리 대역을 확장하기 힘든 것이 메인 스트림 CPU의 약점이 되고 있었다.

그러나 인텔의 패키지 기술 EMIB는 저비용으로 적층 DRAM의 구현을 가능하게 한다. 초고밀도 배선에 의해 수백 GB/s의 광대역 메모리를 실현한다. 그래서 메인 스트림 디스크리트 GPU 수준의 메모리 대역을 메모리 모듈로 사용한 CPU형 제품으로 실현할 수 있다. 메모리 대역 때문에 성능을 제약 받지 않고 내장 GPU 코어를 대형화할 수 있게 된다. 이는 장래에 예상되는 뉴럴 네트워크(액셀러레이터 코어) CPU에 대한 통합에도 중요한 요소다.

세번째는 메모리/스토리지 계층의 변혁이 시작되는 것이다. Kaby Lake-G는 아직 외부 디스크리트 GPU 다이를 사용한다. 그러나 인텔의 본명은 자사의 CPU에 HBM2 인터페이스를 통합하는 세대다. 그 세대가 되면 EMIB로 연결된 HBM2는 CPU의 메모리/스토리지 계층의 일부로 완전히 통합된다.

새 메모리/스토리지 계층의 메모리 대역은 온 패키지 스택 DRAM으로 메모리 용량은 DIMM소켓의 DRAM 모듈에서 벌어진다. 또 DIMM 소켓에 비휘발성 메모리 모듈을 타고 더 대용량의 메모리 탑재가 가능하다. 이를 위한 기술의 변화가 Kaby Lake-G에서 시작된다고 추측된다.

AMD의 움직임에 맞서 움직이기 시작한 인텔의 광대역 메모리 계획

광대역 메모리의 CPU 통합이라는 측면에서 보면 Kaby Lake-G 에는 복잡한 사정이 있었다. 광대역 DRAM의 CPU 패키지 탑재는 원래 AMD가 먼저 움직이기 시작하고 있었다. AMD는 CPU와 GPU의 통합을 진행하고 메모리 대역이 문제가 될 것이라고 생각하여 DRAM 벤더와 "HBM" 스택 DRAM 개발을 진행시키고 있었다. 당초 AMD 구상에서는 하이엔드 GPU 뿐 아니라 메인 스트림 GPU나 APU에도 HBM을 조기에 채용할 터였다.

한편 인텔은 밀접한 관계에 있는 Micron Technology의 스택 DRAM "HMC"의 구상에 타고 있었다. 그러나 HMC는 성격상 서버나 하이엔드 그래픽용 솔루션이 될 전망이었다. 반면 당초 구상의 HBM은 보다 저비용으로 될 예정이어서 HMC와는 다른 레이어가 될 전망이었다. 그래서 인텔은 HMC와 별도로 메인 스트림 PC에 적용할 수 있는 광대역 메모리 솔루션이 필요했다.

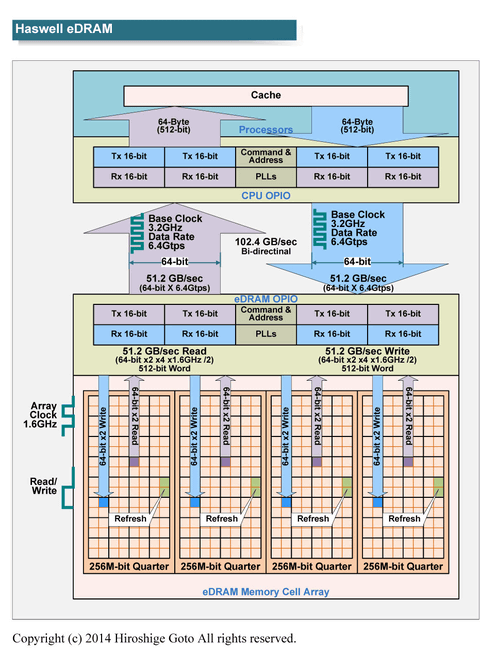

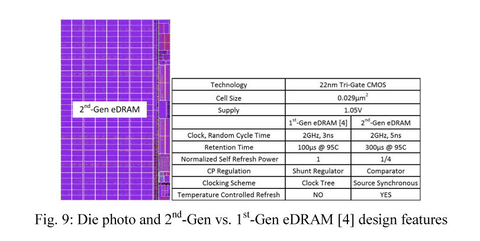

거기서 인텔은 자체 기술로 개발한 eDRAM을 사용, 광대역의 eDRAM 칩을 자사에서 제조하고 CPU 패키지에 탑재하는 방향으로 나아갔다. 커스텀 eDRAM으로써 광대역, 고 효율의 데이터 전송을 실현하고 메모리 킬러인 GPU 코어를 내장하는 진행 방향이다. 그러나 인텔의 eDRAM은 DRAM 셀 크기가 커서 다중 뱅크 구성한 것도 있고, 대용량 화가 어렵다. 이 eDRAM은 본질적으로 논리 칩에 혼재하는 기술로 인텔은 캐시로 채용도 검토했다고 한다. eDRAM 다이는 경제적인 치수에서는 메모리 용량이 한정되므로 용도가 한정되고 만다. eDRAM 다이는 대용량 스택 DRAM이 보급되기까지의 중간적인 솔루션에 불과하다.

그래서 인텔은 eDRAM 버전의 Haswell을 도입하는 한편, JEDEC(반도체 표준화 단체)에서 스택 DRAM "HBM2"의 규격화에 참여, HBM2 스펙을 CPU에 채용하기 쉬운 것으로 바꿨다. 핍박하는 메모리 대역 문제 해결 때문에 eDRAM으로 바꾸고 HBM2를 채택하는 것은 인텔에게 포함된 전략이었다. 실제로 인텔은 DRAM 업체에 대해 HBM2의 채용 예정을 당초부터 설명하고 있다.

HBM2의 준비는 했지만 Intel CPU의 준비가 되지 않았다

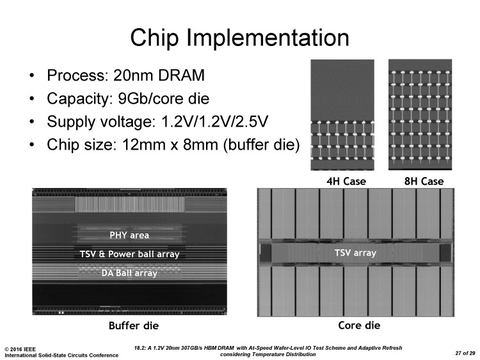

그러나 HBM 규격은 도중에 베이스 로직 다이가 필요한 구성으로 바뀌면서 비용이 예상보다 상승했다. 또 실리콘 관통 전극(TSV:Through Silicon Via) 실리콘 인터포저의 비용이 예상대로 빠르게 떨어지지 않았다.

이 상황에서 DRAM 업계는 TSV 인터포저를 쓰지 않는 HBM 솔루션을 모색하고 있었다. 조밀 배선을 가능하게 하는 인텔의 EMIB는 바로 HBM에 응용할 수 있는 기술이다. 작은 실리콘 조각밖에 쓰지 않는 EMIB는 큰 실리콘 다이에 TSV기술을 사용하는 TSV 인터포저와 비교해 현격하게 비용을 낮출 수 있다. 저비용인 EMIB를 사용하면 TSV 인터포저를 쓰기 위해 고비용으로 메인 스트림 CPU에 적용할 수 없는 HBM을 보급 가격대로 가져올 수 있다. TSV 인터포저의 대체 기술은 또 개발되고 있지만 인텔의 EMIB는 가장 유력한 기술의 한가지다.

인텔은 이처럼 우선 HBM2의 스펙 수립에 참가하여 HBM2를 메인 스트림 PC에 채용하기 쉬운 규격으로 했다. 다음으로 HBM2를 기존보다 저비용으로 통합할 수 있는 EMIB를 실용화했다. HBM2의 생산이 순조롭게 가기 시작하면서 HBM2 채용의 기회가 무르익고 있었다. 그런데 이 스케줄을 따라잡지 못한 것이 한가지 있었다. 그것은 인텔 자신의 HBM2 대응 칩이다.

HBM2 인터페이스를 구현하게 되면 CPU 다이는 현재의 것과는 다른 다이를 새로 설계할 필요가 있다. 인텔의 CPU 로드맵이 자주 변경되고 HBM2 대응이 좀처럼 보이지 않는 상황이었기 때문에 HBM2와 EMIB가 부인 되더라도 인텔 자신이 그것을 활용할 수 있는 칩이(FPGA 이외에는) 없는 상태였다.

Kaby Lake-G은 이 딜레마를 "울트라 C"에서 해결하는 방법이었다고 본다. 타사 다이를 사용하면서 조기에 EMIB 기반의 HBM2 메모리 솔루션을 세운다. 러닝 커브를 높이고 다음 단계에서는 보다 널리 보급한다.

여기서 나오는 의문은 AMD 측의 이익은 무엇인가라는 점이다. AMD에도 상응하는 대가가 없으면 여기까지 이러한 제품 계획은 실현되지 않을 전망이다. 어쨌든 현재 쟁점이 되는 것은 프로세서 제품 그 자체가 아니다. 패키징 기술과 광대역 메모리가 초점으로써 Kaby Lake-G 뒤에는 그 부분에서 인텔의 움직임을 감지할 수 있다.

출처 - http://pc.watch.impress.co.jp/docs/column/kaigai/1054618.html

'글로벌 IT 뉴스' 카테고리의 다른 글

| AMD 라데온RX 500 시리즈 발표, 폴라리스 개선 (0) | 2017.04.19 |

|---|---|

| LG 32UD99 등장, 4K-HDR10, 프리싱크, 999달러 (0) | 2017.04.16 |

| 윈도우10 크리에이터스 업데이트에는 MBR-> GPT 변환 도구 탑재 (0) | 2017.04.16 |

| 엔비디아 타이탄XP 발표, 지포스 GTX 1080TI 보다 빠르다 (0) | 2017.04.08 |

| 애플이 자체 GPU 개발 발표, 이매지네이션 주가 폭락 (0) | 2017.04.08 |