DRAM 다이당 대역폭을 4배로 끌어올린 HBM2

획기적인 새 모드가 추가 된 2세대 HBM

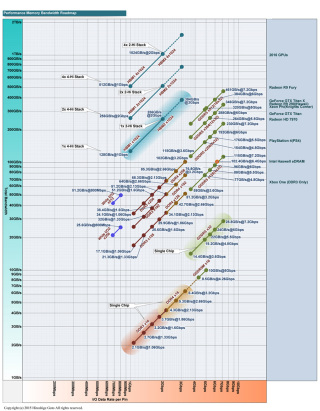

올해(2016년)은 HBM(High Bandwidth Memory)이 본격적으로 전개된다. HBM은 지난해(2015년) AMD의 Radeon R9 Fury(Fiji)계의 제품 패밀리에 채용됐다. 그러나 DRAM 벤더는 SK 하이닉스 한곳에서 채용도 AMD 하나, 그것도 하이엔드 제품에만 채용됐다. 메모리 대역도 GDDR5 베이스의 384GB/sec(512-bit 인터페이스)에 비해 HBM1은 512GB/sec로 33% 증가에 그쳤고 메모리 용량도 GDDR5의 최대 8GB에 비해 HBM 기반 Radeon R9 Fury(Fiji)는 최대 4GB로 반대로 적어졌다. 그 때문에 임팩트는 그리 크지 않았다. 저전력으로 컴팩트 한 Radeon R9 Nano가 빛을 발했지만 HBM이 신기술로 갈채를 받는 일까지는 없었다.

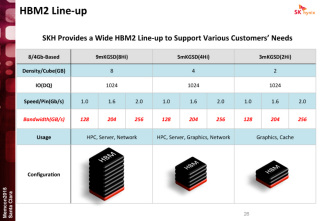

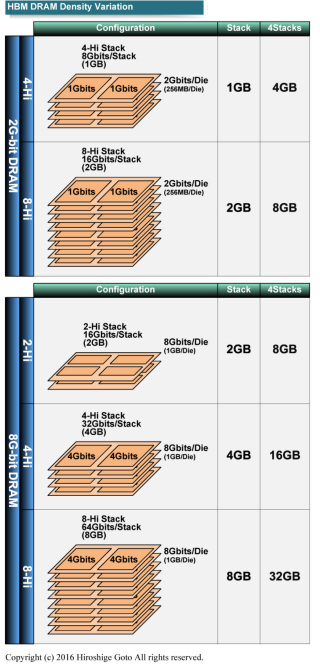

그러나 올해는 2세대 HBM2 기술을 기반으로 한 DRAM이 등장한다. DRAM 제조벤더도 복수, 채용 업체도 AMD 뿐 아니라 NVIDIA 등 여러 업체로 확산된다. 메모리 대역은 1GB/sec로 증가하여 메모리 용량은 최대 32GB(4스택)로 함께 증가한다. 제품 라인도 HBM2 세대에서 퍼포먼스 라인 전체에 확산되기 시작할 가능성이 높다.

HBM규격은 1,024-bit 초 광대역 메모리 인터페이스를 쓴 적층 DRAM 기술이다. HBM1은 전송 속도가 1Gbps였지만 HBM2는 전송 속도가 2Gbps로 오른다. HBM은 DRAM을 적층한 스택 단위로 다룬다. 4스택의 메모리 대역은 HBM1에서 512GB/sec, HBM2는 1TB/sec로 배가된다.

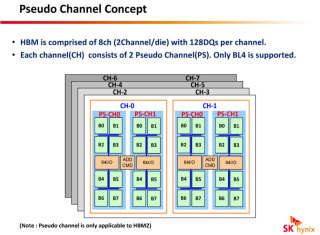

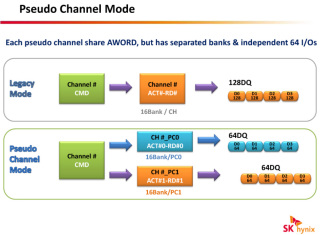

뿐만 아니라 HBM1에서는 1다이당 DRAM 용량이 2G-bit지만 HBM2는 8G-bit 다이가 중심이 된다. 또, 스택은 HBM1이 DRAM 다이를 4개까지 적층했던 것이 HBM2에서는 8개까지 적층 된다. 또, 레이턴시 저감과 대역 확장에 효과가 있는 "Pseudo Channel" 모드도 가세한다. 또 ECC 버전이 HBM에 추가된다.

간단히 말하면 HBM은 2세대가 되고 성능은 증가하여 기능이 충실하며 제조 측면에서도 채용이 진전되지만 그것 뿐만이 아니다. HBM2는 시장을 더 넓힐 수 있는 새 요소가 추가된다. 그것은 1다이당 메모리 대역을 4배까지 향상시킨 모드다.

2개의 다이에 8채널 1,024-bit의 메모리 인터페이스를 지원

AMD의 Joe Macri(Corporate vice president, Product CTO, Corporate Fellow, AMD)는 지난해 12월 Radeon Technologies Group(RTG)Tech Summit시에 다음과 같이 HBM2에 대해서 설명하고 있다.

"HBM의 이점은 폼 팩터와 전력에서 제곱mm당의 대역을 현저하게 증대시키는데 있다. HBM2는 그러한 HBM의 이점을 더욱 발전시킨 규격으로, 2배의 전송 속도다. 그러나 HBM1에서 HBM2로의 변화는 대역만이 아니다. 가장 훌륭한 변화는 스택의 계층 수를 줄일 수 있게 된 것이다. HBM1에서는 4-Hi(4층)스택이 아니면 풀 메모리 대역을 얻지 못 했다. 반면 HBM2에서는 2-Hi(2층)의 스택으로 풀 대역을 얻을 수 있다. 대역 때문에 4-Hi에서 DRAM 다이를 4층으로 해야 한다는 제약이 없어졌다. 더 유연하게 넓은 범위의 제품에 대응할 수 있게 됐다"

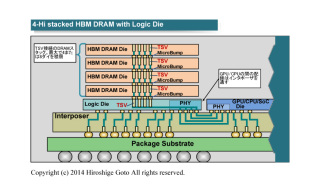

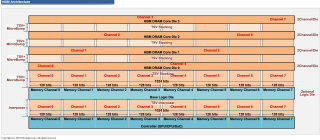

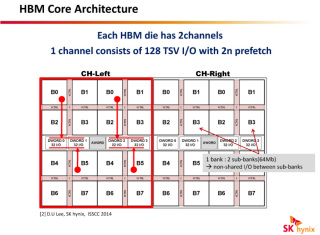

왜 HBM1에서는 4-Hi 스택이 아니면 풀 대역을 달성하지 못했는가, 그것은 HBM DRAM의 다이당 채널 폭이 2채널이었다. HBM은 128-bit 너비의 독립된 메모리 채널을 8채널 묶은 사양으로 되어 있다. 128-bit의 채널이 8채널에서 합계 1,024-bit로 이를 1Gbps에서 구동하고 128GB/sec의 대역을 얻는다.

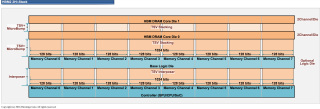

그러나 HBM1에서 1개의 DRAM 다이는 2채널까지만 지원할 수 없다. 그래서 4개의 DRAM다이를 적층한 4-Hi 스택이 아니면 1스택당 128GB/sec의 대역을 얻을 수 없다. 2-Hi 스택에서는 절반인 4채널 밖에 적용되지 않기 때문에 메모리 대역은 64GB/sec다. HBM2는 이 부분을 개량했다고 한다.

"HBM2에서도 기본은 4개의 다이로 8채널 폭이다. 그러나 HBM2는 2-Hi 스택의 경우는 2개의 다이에서도 8채널 폭이 가능하도록 했다. HBM1은 8채널 폭에는 반드시 4개의 다이가 필요했다. 여기가 큰 차이로 적은 DRAM 다이 개수로 풀 대역을 얻을 수 있게 된다"

2-Hi 스택으로 풀 대역의 구성은 지난해 10월 메모리 콘퍼런스 memcon에서 SK 하이닉스가 밝히고 있다. SK 하이닉스의 슬라이드에서 2-Hi 스택에서도 2Gbps 메모리 대역은 256GB/sec다. 기존의 스펙이라면 2-Hi 스택의 대역은 128GB/sec 이다.

기존의 설계 변경을 최소화한 2-Hi 스택

DRAM 벤더가 2-Hi 스택에서 풀 대역 구성 형태에 대해 이야기하기 시작한 것은 지난해 후반부터다. 처음에는 그런 설명은 하지 않았고 이후에 추가된 사양임을 알 수 있다. HBM2 제품은 처음부터 2-Hi 구성 형태가 지원된다. Macri는 DRAM 벤더 측에 대응하도록 설계를 쉽게 했다고 한다.

"메모리 벤더는 DRAM 제조에서 위험을 싫어한다. 그래서 설계에 있어 변경을 최소화하고 또 설계를 공통화함으로써 리스크를 낮출 필요가 있었다. (2-Hi와 4-Hi) 2개의 설계를 1개로 하는 것으로 HBM 설계의 위험을 줄였다. (2-Hi 스택으로 풀 대역은) 아직 정식(JEDEC) 스펙으로는 되지는 않았다. 정식으로 되지 않는 것은 이 사양이 불 필요하다고 생각하고 있는 사람들도 있기 때문이다. 그러나 DRAM 벤더는 이미 대응한 설계로 진행했다"

HBM2에서 1다이에 2채널 구성과 4채널 구성에서 HBM DRAM의 다이 자체는 마찬가지가 될 것으로 보인다. 그렇다면 DRAM 벤더들은 2가지의 다른 DRAM 다이를 설계&제작할 필요가 없어지고 투자와 위험이 적어진다. 단, 다이의 메모리 뱅크 수는 바뀌지 않을 것으로 보인다. 그 경우 채널당 메모리 뱅크 수는 반감될 가능성이 있다.

그러나 HBM2에는 Pseudo Channel 기능이 있고 원래 뱅크를 분할하고 2개의 Pseudo Channel 에 할당하여 쓸 수 있다. HBM2는 레거시 모드에서 1채널당 16뱅크로 Pseudo Channel 모드에서는 1 Pseudo Channel 당 16채널이다. 1다이에 4채널 모드시에는 이 기능을 조합함으로써 뱅크 충돌을 낮출 수 있다. 이러한 HBM2는 처음부터 기능을 잘 사용하면서 공통 설계화하고 설계와 제조 비용을 낮추는 방법을 취했다고 추측된다.

HBM2는 핀당 전송 속도는 HBM1의 2배가 되었다. 더불어 다이당 채널 수도 배가하는 구성이 가능했다. 그래서 다이당 전송 대역은 HBM1의 피크에서 2배에 이른다.

"HBM1에서는 4개의 DRAM 다이를 사용한 1개의 4-Hi 스택으로 메모리 대역은 128GB/sec였다. HBM2는 전송 속도가 HBM1의 1Gbps에서 2Gbps로 2배로 올랐다. 그 위에 2-Hi 스택으로 풀 대역을 얻을 수 있게 되었기 때문에 4개의 DRAM 다이를 사용한 2개의 2-Hi 스택에서 512GB/sec의 메모리 대역을 얻을 수 있다. 다시 말하면 HBM2의 다이당 메모리 대역은 HBM1의 4배다. 같은 수의 DRAM 다이로 4배의 대역이 달성된다. 놀라운 메모리 대역 효율이다. 그리고 다이수가 적으면 그 만큼 비용이 낮아진다. 그래서 HBM2는 대역당 비용 면에서도 효율적이다"(Macri)

HBM2를 CPU 나 APU 캐시에 채용하는 길이 열려

HBM2의 2-Hi 스택 구성이 중요한 것은 HBM2를 미들 레인지 GPU 제품이나 최종적으로는 APU(Accelerated Processing Unit)에도 채용할 수 있는 길이 열린 것이다. 보다 작은 메모리 입도에서 광대역이 가능하므로 제품 가격을 생각한 카테고리의 제품이나 캐시적인 방법을 사용하는 제품에도 확대할 수 있게 된다.

HBM1에서는 DRAM의 다이당 용량은 2G-bit 였기 때문에 4-Hi 스택에서 스택 용량이 1GB, 4개의 스택에서 합계 4GB로 용량이 고정되어 있었다. 반면 HBM2는 DRAM 다이당 용량은 현재 8G-bit다. 따라서 4-Hi 스택을 4개 사용하면 스택당 4GB 용량으로 합계 16GB 용량이다. 16GB 밖에 선택할 수 없다고 한다면 그래픽 용도에서는 도입이 불편하다.

그러나 HBM2에서는 2Hi 스택으로 풀 대역을 갖는다. 그래서 2-Hi 스택을 4개 사용한 1TB/sec으로 8GB의 메모리 구성도 가능하다. 혹은 2Hi 스택을 2개 사용한 512GB/sec로 4GB 메모리 구성의 GPU도 가능하다. 그것은 2Hi 스택 하나만 256GB/sec로 2GB로서 APU 캐시적인 사용법의 구성을 취하는 것도 가능하다. HBM은 2세대 만에 시장 범위를 넓힐 수 있게 된다.

"HBM에서는 메모리 대역을 메모리 용량보다 우선하여 설계했다. HBM1은 웬만한 메모리 용량에서 매우 넓은 대역이 되었다. 하지만 향후의 HBM에서는 2-Hi에서 저용량도 있고 능력이 필요한 경우에는 스택을 8-Hi로 거듭함으로 늘릴 수 있다. 그래서 용량보다 대역을 우선하는 소비자 시장에서 용량을 중시하는 HPC나 워크스테이션 시장까지 넓게 커버할 수 있게 됐다"고 AMD의 Macri는 말한다.

실제로 HBM2가 먼저 확산되는 곳은 GPU 컴퓨팅 등의 시장이 될 것이다. HPC(High Performance Computing)의 슈퍼 컴퓨터 시장 및 초 광대역이 요구되는 네트워크 시스템 등의 임베디드 기기 등이 최초의 HBM2 시장으로 예상된다. 하지만 HBM2는 사양은 보다 넓은 시장으로 확대될 수 있게 됐다.

출처 - http://pc.watch.impress.co.jp/docs/column/kaigai/20160128_740790.html

'글로벌 IT 뉴스' 카테고리의 다른 글

| 남 대서양 횡단 해저 광케이블 건설 시작 (40Tbps) (0) | 2016.04.22 |

|---|---|

| 스카이레이크 내장그래픽 성능, 실행 모델을 변경 (0) | 2016.04.22 |

| AMD, 브리스톨릿지 7세대 APU를 5월말 투입 (0) | 2016.04.22 |

| 칩웍스, 아이폰SE 분해 리포트 공개 (0) | 2016.04.22 |

| 2016년 4월 마이크로소프트 보안 패치 (0) | 2016.04.22 |